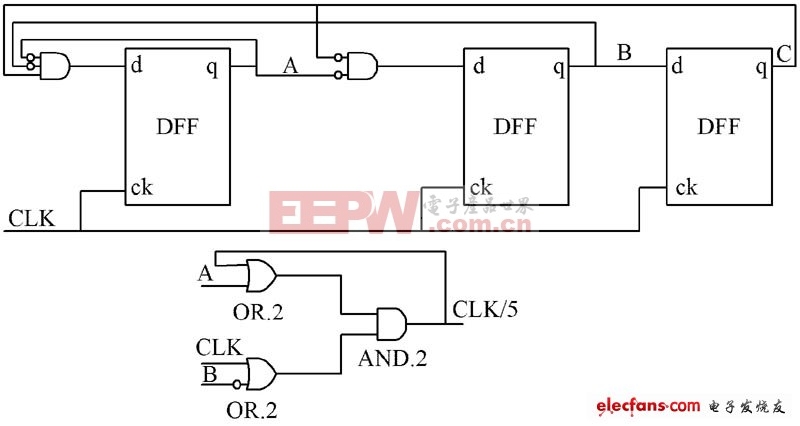

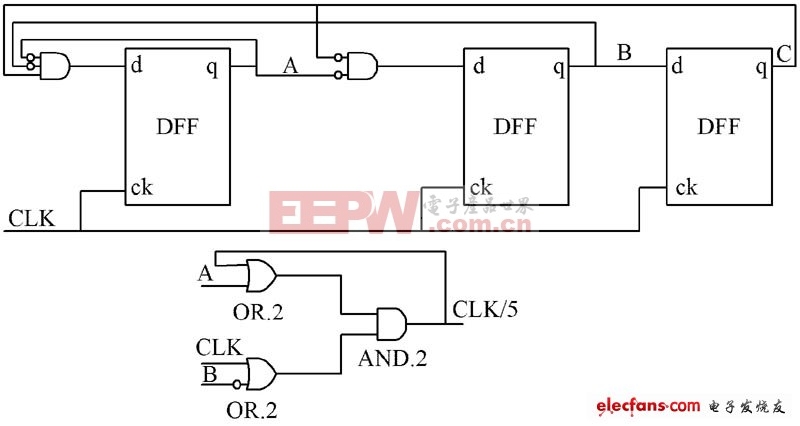

D触发器结构的五分频器逻辑电路

D触发器结构的五分频器逻辑电路由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B, 然后对时钟信号CLK, A 和B 进行逻辑运算得到占空比为50% 的五分频信号CLK/ 5, 其计数过程如表1 所示, 从表1 的计数过程可知, 分频后的时钟CLK/ 5 的周期是输入时钟CLK 的5 倍, 由此实现了五分频并且其占空比为50% .

D触发器结构的五分频器逻辑电路由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B, 然后对时钟信号CLK, A 和B 进行逻辑运算得到占空比为50% 的五分频信号CLK/ 5, 其计数过程如表1 所示, 从表1 的计数过程可知, 分频后的时钟CLK/ 5 的周期是输入时钟CLK 的5 倍, 由此实现了五分频并且其占空比为50% .

评论