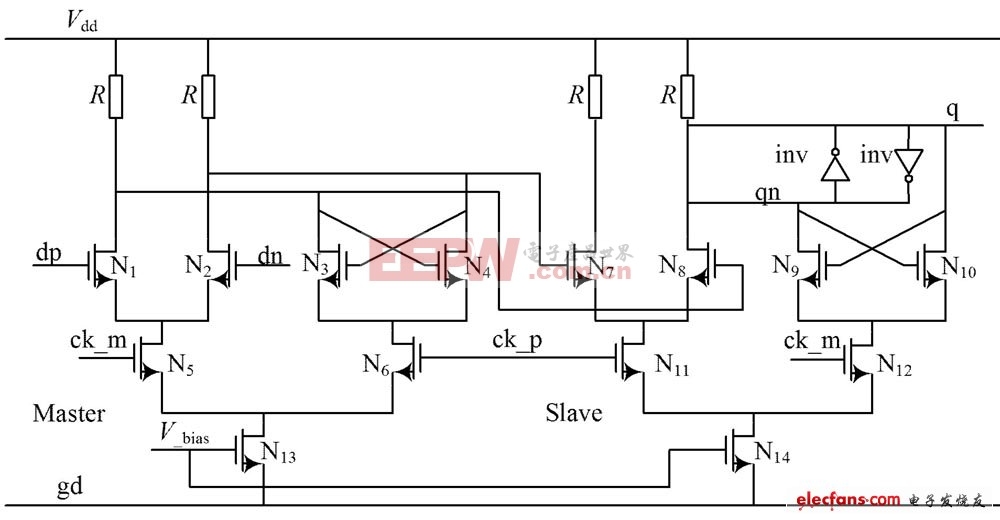

CML锁存器构成的主从式触发器电路

该触发器由2 个CML 结构锁存器组成, 它们构成主从型结构, 每个锁存器都要经过2 个阶段: 跟踪阶段和保持阶段。当主锁存器跟踪输入信号时, 从锁存器处于锁存保持阶段, 然后交替。其中N13 , N14 为尾电流管, 偏置电压V_bias 使N13 , N14管工作在饱和状态, 充当恒流源的作用。dp 和dn 是由输入信号d 经传输门和反相器产生的一对互补差分信号, ck_m 和ck_p 是由输入时钟信号clk 经传输门和反相器产生的一对互补时钟差分信号。主锁存器工作状态为: 当ck_m 为高电平时, N5 管导通, N6 管关闭, 此时N1 , N2 管工作在差分状态, 将输入信号dp, dn 采入。当ck_p 为高电平时,N6 管导通, N5 管关闭, 此时N3 , N4 使电路维持在锁存状态, 从锁存器工作状态恰好与主锁存器工作状态相反。设计中在触发器输出端q, qn 之间加了2 个反相器从而在q, qn 之间形成正反馈, 增强了电路的输出驱动能力。工作时, 电路的尾电流应当足够大, 有利于提高电路工作频率和输出信号的摆幅。

评论