A3936引脚图及引脚功能介绍

A3936引脚图及引脚功能介绍

引脚介绍

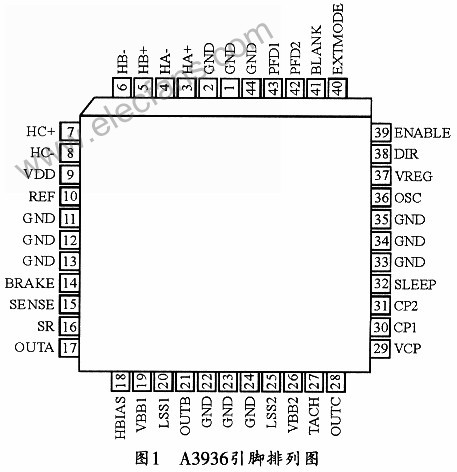

A3936芯片采用44脚PLCC封装型式,其引脚排列如图l所示。各引脚的功能如下:

引脚1、2、11、12、13、22、23、24、33、34、35、44(GND):接地端;

引脚3、4、5、6、7、8(HA、HB、HC):无刷直流电动机HALL元件信号输入端;

引脚9(VDD):+5 V电源;

引脚10(REF):参考电压VREF输入端,通过控制该电压可控制PWM占空比;

引脚14(BRAKE):制动控制端,当该脚为高电平时,无刷直流电动机内的电流会瞬间释放,电机突然停转;而在正常使用时,该脚接低电平;

引脚15(SENSE):采样电阻RS引脚,其数值一般取0.1 Ω。该采样电阻与VREF可决定电动机的负载电流。

引脚16(SR):同步整流输入,高电平有效;

引脚17、2l、28(OUT):无刷直流电动机A、B、C相驱动输出端;

引脚18 (HBIAS):HALL元件的负极;

引脚19、26(VBB):负载电源;

引脚20、25 (LSS):通过采样电阻RS与负载电源地相连;

引脚27 (TACH):速度输出,一般悬空不用;

引脚29 (VCP):充电电容连接端,应通过0.22μF/50 V电容与VBB相连;

引脚30、3l(CPl、CP2):电荷泵电容连接端,二者应通过0.22μF/100 V电容相连;

引脚32 (SLEEP):睡眠模式逻辑控制输入端,低电平输入时,进入睡眠模式;

引脚36 (OSC):振荡信号连接端,可通过51kΩ电阻与VDD相连;

引脚37 (VREG):整流去耦端,应外接0.22 μF/50V去耦电容;

引脚38 (DIR):方向控制逻辑输入端,低电平为顺时针旋转,高电平为逆时针旋转;

引脚39 (ENABLE):使能控制逻辑输入端;

引脚40 (EXTMODE):外接PWM控制模式逻辑输入端。使用外接PWM控制模式时,若输入高电平,为电流慢衰减模式;若输入低电平,则为电流快衰减模式;

引脚41 (BLANK):为死区逻辑控制输入端;若输入高电平,死区时间为12/fosc;若输入低电平,死区时间为6/fosc;

引脚42、43(PFD):PFD逻辑控制输入端,二者组合可用于决定采用哪一种续流控制模式。

评论