基于ADF4106的锁相环频率器研究与设计

摘要:本文由锁相环频率合成器的基本工作原理入手,介绍基于锁相环芯片ADF4106的工作特性,并结合环路滤波器、压控振荡器和射频通路设计出一种输出频率为2GHz的频率合成器,并经过印制板加工及测试,验证实验结果满足设计指标。

引言

频率合成器[1-2]的功能就是给收发机中的变频电路提供频率可编程的本地载波信号,是无线收发机的核心模块之一,其性能对通信系统的通信质量具有重大影响。目前频率合成器主要有直接模拟频率合成技术(DS)、锁相环频率合成技术(PLL)、直接数字频率合成技术(DDS)、混合频率合成技术四种实现方式,其中锁相环频率合成器是射频电路中最常使用的一种结构,相比于其他几种结构,PLL结构能够在有限的功耗限制下合成高性能的载波信号。本文基于锁相环芯片ADF4106设计了一种数字锁相环频率合成器,具有超宽的带宽、较好的噪声特性、快速锁定时间,以及功耗低和体积小等特点,从而被广泛应用于无线通信系统中。

1 锁相环频率合成器的基本工作原理

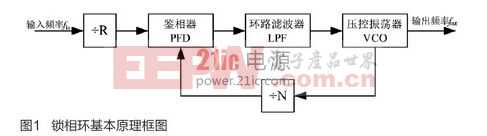

锁相环(PLL)是一个相位误差控制系统,通过将输入信号与压控振荡器(VCO)输出信号之间的相位进行比较,产生相位误差电压经处理后去调整压控振荡器的相位。当环路锁定时,输入信号与压控振荡器输出信号频差为零,相位差不再随时间变化,此时误差控制电压为一固定值,压控振荡器输出频率与输入信号频率相等,即fout=(N/R)*fin。锁相环基本原理框图如图1所示。

锁相环主要结构由VCO、鉴相器(PFD)、分频器和环路滤波器(LPF)组成。其中,PFD主要功能是进行相位比较的,它把VCO输出信号N分频后与输入频率R分频后进行比较,产生误差控制电压。LPF的作用是滤除误差电压中的高频成分和噪声,以保证环路所要求的性能,提高系统的稳定性。VCO受控制电压的控制,使其输出频率向参考信号的频率靠近,两者频率之差越来越小,直至消除频差而相位同步实现锁定。在实际设计中,可以通过程序改变分频比R、N,从而获得需要的稳定输出频率。

2 方案设计与实现

2.1 锁相环芯片ADF4106结构功能介绍

ADF4106是ADI公司生产的集成锁相环频率合成器芯片,利用该芯片可以实现无线收发机上变频和下变频部分的本地振荡。ADF4106由一个低噪声数字PFD、一个精确的电荷泵、一个可编程基准分频器R(14位)、可编程A(6位)、B(13位)计数器和一个双模前置分频器P/P+1组成。A、B计数器和双模前置分频器相连接实现一个分频器N,且N=PB+A。该芯片具有6GHz的频率带宽,2.7V~3.3V的供电电压,独立的电荷泵供电电压,可编程的双模前置分频器P/P+1,其值可取8/9、16/17、32/33和64/65,同时还具有三线串行接口、模拟数字锁定检测、硬件软件低功耗模式等特性。ADF4106同外部LPF和VCO可以组成一个完整的PLL电路。由于ADF4106的宽带特性消除了许多高频系统中倍频器的使用,从而简化了系统结构和降低了成本。

在本文设计中,设计实现2GHz的频率合成器,且要求2GHz频率信号分两路输出,并保证其中一路输出信号功率达到13dBm。该电路主要由ADF4106、LPF、VCO和射频信号输出部分组成。根据图1,选取输入信号频率fin=10MHz,该信号在进入ADF4106的Refin引脚前通过一个T型匹配网络来实现阻抗匹配。为了保证PFD输入信号频率为1MHz,需要通过编程设定基准分频器R的值为10,分频器N的值为2000。

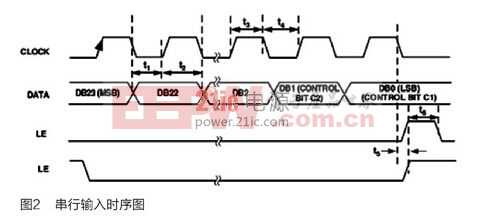

ADF4106具有一个简单的SPI兼容串行接口向器件引脚CLK、DATA、LE写数据,当LE为上升沿时,将CLK每个时钟上升沿存储到寄存器中的24位数据送入合适的锁存器中。串行输入时序图如图2所示。

2.2 LPF设计

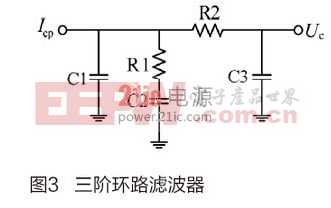

LPF在频率合成器设计过程中直接影响到频率合成器的相位噪声和转换频率,由于PFD的输出不但包含直流控制信号,还有一些高频谐波成分, LPF通过对电阻电容进行适当的参数设置,可以滤除高频成分,避免这些谐波对下一级VCO电路产生影响。LPF可以分为有源滤波器和无源滤波器,本文设计的无源LPF将电荷泵输出电流转换成控制电压,同时抑制鉴相频率的输出纹波。在电路设计过程中,由于二阶LPF很难抑制环路带宽频率十倍以上的纹波,所以采用三阶LPF[3],提高对杂散频率的抑制程度。三阶LPF的电路图如图3所示,对于LPF中电容和电阻的数值,可以通过Analog器件公司(ADI)提供的LPF仿真软件ADIsimPLL和安捷伦公司(注:现更名为是德科技公司)的ADS仿真软件进行仿真得到,通过设定相关参数,并经过不断的优化和调试得出LPF各器件参数值为:C1=100pF,C2=1.5nF,C3=20pF,R1=4.3kΩ,R2=6.2kΩ。

2.3 VCO功能介绍

VCO作为一个电压频率转换器,由于其能够产生最终输出信号频率,所以在PLL中占有重要地位。VCO是一种具有线性控制特性的调频振荡器,其输出频率随控制电压的改变而改变,使输出信号频率向参考信号的频率接近,直至消除频差实现锁定。

VCO [4]具有相位噪声、频率稳定度、频率范围、谐波抑制等器件特性。本文从设计指标要求考虑,选取Z-Communications公司的CRO2000作为压控振荡器,由于该器件具有较低的相位噪声、很好的谐波抑制、较好的线性度以及容易焊接的器件封装,故选取该器件作为PLL的VCO,并在实际应用中取得良好的性能。

2.4 射频通路设计

由于VCO输出负载阻抗为50Ω,故要求2GHz输出信号射频走线阻抗[5]同样为50Ω,本文印制板使用叠层的方式,其中第一层介质材料为Rogers4350B,板厚为20mil,介电常数为3.48,通过仿真软件Polar Si9000计算得到射频走线宽度为40mil。射频通路设计框图如图4所示。

本文要求2GHz频率信号通过Y型电阻式功分器分两路输出,并保证其中一路输出信号功率达到13dBm。由于VCO输出信号功率较小,需要在通路中加入放大器ERA-5SM,保证输出功率值,同时为了抑制2GHz信号之外的谐波和非谐波等干扰,需要在两个通路输出端加上低通滤波器LFCN-2000。

2.5 锁相环频率器电路原理图及测试结果

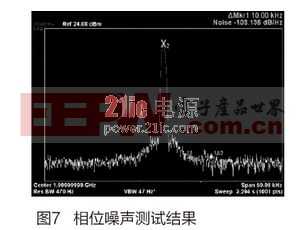

基于上述锁相环频率器各模块的介绍和设计,最终电路设计如图5所示。根据图5所示原理图,画出相应的PCB外协加工,将加工的印制板安装到提前设计好的屏蔽盒中进行测试,安捷伦N9020A测试结果如图6、图7所示。其中图6为输出信号功率测试结果,图7为相位噪声测试结果。

由图6可知,在输出信号2GHz处功率为14.22dBm,满足信号功率达到13dBm的要求。同时由图7可知,输出信号单边带相噪为-103.136dBc/Hz@10kHz处,同样满足设计指标。

3 总结

频率合成器在现代通信系统中具有举足轻重的地位,其性能的好坏决定了通信系统的性能指标。本文基于锁相环芯片ADF4106设计的频率器具有低噪声、低功耗、低成本及电路结构简单等特点,从而被广泛应用于无线通信系统领域。

评论