SiC技术构筑Green未来,Cree引领SiC技术发展

了解SiC肖特基的演变是选择器件的关键

在越来越多的功率电子学应用中,碳化硅 (SiC) 功率器件日益普遍,尤其是在太阳能逆变器的设计中。设计工程师尤为青睐 SiC 肖特基二极管,用于开发新的逆变器设计,因为这比采用硅功率器件的逆变器更紧凑、更高效、更可靠。

自从 SiC 二极管引入市场十多年来,无论是器件设计还是可靠性参数都经历了巨大的演进变化。这些变化为商业市场带来了更广泛的 SiC 肖特基二极管产品组合。因此,眼光敏锐的设计工程师应当知道这些二极管之间的差别,并在设计阶段考虑这方面的因素。

从肖特基势垒到结势垒,再到混合 p-i-n 结构,本文讲述了现代 SiC 肖特基二极管的演变特点,以及它们在性能、可靠性和坚固性上的差别。我们的讨论以 Cree 器件为例,但读者应注意,本文所述的各类器件有着多种来源渠道。

早期SiC 肖特基势垒二极管的高电压弊病

如同任何产品,当今市场上 SiC 肖特基二极管的质量和性能也是参差不齐。这在很大程度上取决于器件的实际结构。先来谈谈简单的肖特基势垒二极管的结构。

肖特基势垒二极管 (SBD) 是最简单的半导体器件之一。最基本形式的 SBD 由一个金属-半导体结所组成。最初 SiC 肖特基二极管就是采用这种结构。但是这些简单的器件很快就在实际应用中遇到了问题。[1,2]

人们对 SiC 肖特基二极管的关键要求之一,就是它必须能反向阻挡高电压 (>300 V)。然而早期的 SiC SBD 被发现存在一个缺陷,就是漏电流随着时间逐步增大,直至器件发生毁灭性的故障。[1]

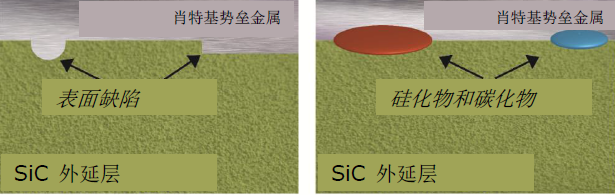

在设计过程中,有许多与肖特基势垒相关的因素造成了这种固有缺陷(图 1)。通过肉眼观察,可以发现 SiC 外延层存在表面缺陷和不平整,当肖特基金属沉积在其上时,就会造成巨大的结构缺陷。另外,两种材料之间的界面可能形成种种硅化物和碳化物。

图 1. SiC 基质与肖特基势垒金属之间的典型表面接触缺陷。

从微观角度来说,肖特基金属和 SiC 半导体具有不同的晶体结构和晶格参数,所以会在结合处造成严重的原子级的不调和。这些因素导致了整个结平面的结构缺陷。在反向状态,这些缺陷就成为漏电流的导火索。另外,由于漏电流引起局部温度上升,这些缺陷会逐渐扩大[3]。缺陷越大,漏电流越多,如此交替发展,直至器件最终无法阻挡额定电压。

结势垒设计改善可靠性

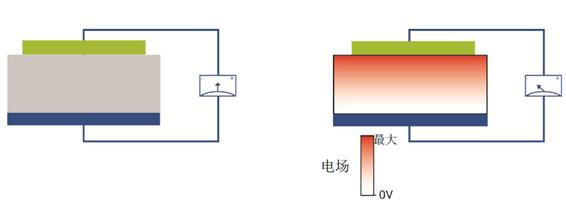

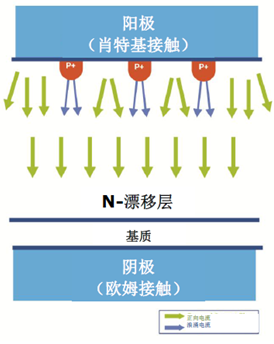

这个问题的解决办法是引入一种设计,称为“结势垒肖特基”(简称“JBS”)。[4]JBS 设计的主要改进是在肖特基势垒下面加入了均匀间隔的 p+ 阱。从图 2 可见,这种改进显著提高了二极管的可靠性和坚固性。

图 2a 所示为反向状态的基本型 SBD。电场梯度沿着 n-漂移层的厚度分布,电场峰值发生在势垒处,刚好就是缺陷之处。如果是 JBS 二极管,p+ 阱就会与周围的 n-漂移层形成连串的同质结。

图 2a. 纯肖特基二极管反向状态下(右)的结构(左)和电场分布。

图 2b. JBS 二极管反向状态下(右)的结构(左)和电场分布。

和任何半导体结一样,在 p+ 阱和 n-漂移层的界面存在着一个耗尽区。当肖特基二极管处于反向状态,p-n 耗尽区的电场就会撞击外加电场。如图 2b 所示,合成峰值电场位于 p+ 阱底,远离肖特基势垒的缺陷处。因此,和基本型肖特基势垒二极管相比,JBS 二极管的漏电流大为减少,击穿电压明显提高。

混合P-I-N 结构增强瞬变电流处理

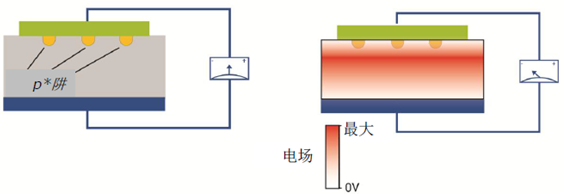

在产品创新及持续开发十余年后,SiC 结势垒肖特基二极管又演变为“混合 p-i-n 肖特基”(简称“MPS”)。[5]MPS 二极管具有 JBS 二极管反向状态下的所有优点,而且融入一种正向状态下所独有的特性。

在 MPS 结构中,p+ 阱经过改造,和基质材料一起形成了 p-i-n 结。在正常的正向工作中,这些 p-i-n 结处于不活动状态,因此不产生正向电流。一旦发生正向瞬变情况,p-i-n 结就会开启,从而大幅提高二极管的正向电流承载能力(图 3)。这使得器件的正向浪涌电流处理能力相比简单的肖特基二极管大为增强。

图 3. 瞬变浪涌状态下 Cree MPS 二极管结构图。

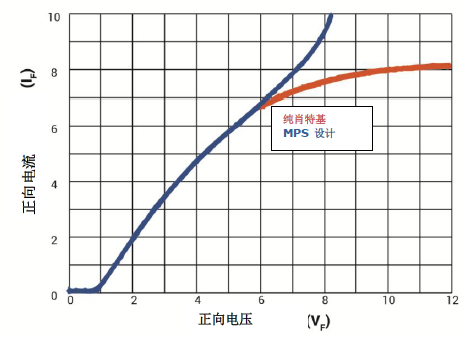

图 4 比较了 MPS 二极管和纯肖特基二极管在正向电流下的曲线绘图仪测量值。在高浪涌电流状况下,受较高的正向电压降影响,纯肖特基二极管会发生热逸溃,并且可能损毁。而在同样状况下,MPS 二极管能够传输同样的高电流,但正向电压降只有轻微增加,所以要比纯肖特基二极管坚固得多。

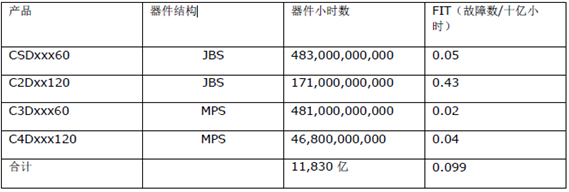

现场数据支持了这个结论。Cree 提供商用 JBS 和 MPS SiC 二极管已有十余年,这些器件的现场使用时间累积约达 1 万亿小时。它们的总单位时间故障率 (FIT) 为 0.095,还不到历史悠久的硅器件可比数值的二十分之一(表 1)。

图 4. MPS 二极管(蓝线)和非 MPS 二极管(红线)的曲线绘图仪测量值。p-i-n 二极管激活使 MPS 二极管的曲线在 6V 以上继续向上延伸。

表 1. Cree SiC MPS 和 JBS 肖特基二极管的 FIT 数据

近年来,纯 SBD 器件在 SiC 肖特基二极管市场再度兴起,为消费者提供了更低价格的选择。也许这些厂商针对原先 SiC SBD 器件的故障模式找到了令人满意的解决方案,但是如今的 SBD 依然存在固有缺陷,那就是峰值电场位于肖特基结。所以和 MPS 二极管相比,它们的漏电流依然偏高,击穿电压则偏低。

除此之外,它们也完全不具备像 MPS 二极管那样先进的正向浪涌保护能力。理论上,表 1 当中本应纳入 MPS 与 SBD 器件的 FIT 数据比较。但是,由于商用 SiC SBD 器件投入市场的时间尚且不长,所以现场数据颇为有限。近期分析揭示,这种新型的纯肖特基二极管经过连续雪崩测试后会出现工作不稳定的现象,而在 MPS 器件中则未发现这种情况。[6]

那么,消费者应该如何判断自己所购买的是 SBD、JBS 还是 MPS?器件厂商未必会说明他们生产的 SiC 二极管属何结构,不过消费者一般可以索要这方面的资料。如果无法获得资料,可以通过数据表内相关数值的快速比较,了解器件结构。

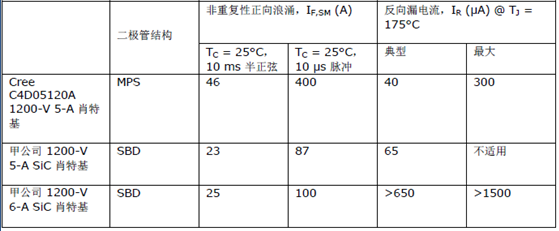

例如,简单 SBD 器件的反向漏电流要高于同类 JBS 和 MPS 器件,尤其是温度升高时。而 MPS 二极管的正向浪涌额定值则高于 JBS 和 SBD。由于测量参数的不同,这些产品的差别很难量化,不过 MPS 的浪涌一般至少比同类 SBD 高出两倍。

例如,表 2 比较了 Cree MPS 二极管与典型的商用 SBD 二极管的数据表数值。

表 2. Cree MPS 二极管与商用 SiC SBD 二极管的比较。(下列比较以已公开的数据表中的规格为依据。)

进一步而言,进取型的工程师可以收集每种二极管的几个样品,送到实验室测试,从而深入了解数据表中通常所不能反映的器件状况。如图 5 和图 6 所示,在极端正向和反向状态下,二极管的结构便可一目了然。

在相当于额定电流 5 倍至 10 倍的正向状态下,由于 p-i-n 二极管开启,MPS 器件呈现出一条向上的抛物线。相反,随着器件饱和并趋于失效,SBD 器件的曲线渐趋平缓。另外,在反向状态下,SBD 的漏电流高于 JBS/MPS 器件,而击穿电压则低于 JBS/MPS 二极管。

图 5. 正向状态下 Cree 10-A MPS 二极管与甲公司 10-A SBD 二极管的比较。

图 6. 反向状态下 Cree 650-V MPS 二极管与甲公司和乙公司 650-V SBD 二极管的比较 (125°C)。

结论

所有的新技术都必须经受一个完整的技术生命周期的考验。采用结势垒肖特基或者混合 p-i-n 肖特基结构的 SiC 肖特基二极管,在商业市场上已经有十多年的历史。因此,可以说这类二极管已经达到生命周期的成熟阶段,当初它们投放市场后的种种问题和场失效缺陷,早已得到解决。反观纯 SiC 肖特基势垒二极管虽然比 JBS 和 MPS 二极管更早投入使用,但是现有的 SBD 器件依然处于引入期,原因就是从它们当初引入到近期重新进入商业市场,这中间相隔了漫长的时间。

尽管部分 SBD 厂商已经推出二代产品,但其中许多仍属于第一次设计迭代。我们没有理由怀疑这些厂商不会尽全力生产高质量的可靠产品,但是这些相对年轻的技术难免会有更高的早期型失效的风险,而且遗憾的是,由于现有的 FIT 现场数据颇为有限,因而无法做出确切的结论。

诸如 Cree 等公司供应的商用 SiC MPS 二极管,现已达到第五次设计迭代,而且大量的现场数据都证明了这种设计的高度可靠性。MPS 设计兼具更强的浪涌能力和更高的击穿电压,借助这种坚固、耐用、可靠的成熟技术,工程师们就可以放心地设计自己的产品。

评论