TMS320F240中文资料

TMS320F240 简介

TMS320F240 为TI 公司所出品的定点式数字信号处理器芯片,

具有强大的外围(64k I/O space、10 bit A/D Converter、Digital I/O

peripheral) ,芯片内部采用了加强型哈佛架构(Enhanced Harvard

Architecture),由三个平行处理的总线─程序地址总线(PAB)、

数据读出地址总线(DRAB)及数据写入地址总线(DWAB),使其能

进入多个内存空间。由于总线之操作各自独立,因此可同时进入

程序及数据存储器空间,而两内存间的数据亦可互相交换,使得其

具有快速的运算速度,几乎所有的指令皆可在50ns 周期时间内执行

完毕,内部的程控以管线式的方式操作(Pipeline operation),且使

用内存映像的方式,使其整体的效能可达到20MIPS,因此非常适

用于实时运转控制,而对于速度较慢的外围亦提供了wait-states 的功

能。TMS320F240 单芯片硬件架构上的一些特性对于高速信号处理及

数字控制上的应用是必须且重要的,其使用次微米CMOS 技术制程

使其功率散逸降至最低。其与传统的微处理机单芯片相较之下其具有

下列的优点:

(1)执行速度快,整体效能佳,可达到真正的实时控制。

(2)特殊的硬件及指令设计,适用于高性能的控制。

(3)容易增加附属功能,很容易扩展外围。

(4)具有实时中断的看门狗定时器模块,可监控程序之运作。

(5)使用4 层的Pipeline 的程序运作及设计有指令延迟之功能。

TMS302F240 架构介绍

TMS302F240 单芯片的硬件架构是以16 位为基本数据处理单

元,采用16 位的数据与地址总线,其指令集设计成可大范围且

复杂的计算及高速处理,属于Memory Mapping 的模式,主要架构如

下表所示:

项目 | 说明 |

中央处理单元 | .32位的算数逻辑单元 |

内存单元 | .16K word 芯片上的程序内存 |

程控单元 | .4个管线式的操作 |

指令设计 | .采用定点式运算 |

事件处理器 | .12个脉波宽度调变信号的输出 |

外部外围 | .2个相位编码电路 |

中央处理器

TMS320F240 单芯片之中央处理器因为其平行结构之设计,使得

在单一指令周期内可执行高速运算。中央处理器之内部主要可分为三

单元:输入倍率区段、乘法区段、中央运算逻辑区段。

1. 输入倍率区段

TMS320F240 芯片上共有三个硬件16 位的倍率位移器,这些

倍率位移器具有将数据放大(左移)或缩小(右移)的功能,第一个倍率

位移器可以称为数据倍率位移器(Input Data-Scaling Shifter),位于输

入倍率区段内,它的输入端是直接连至16 位的数据总线,而输

出端则是接到32 位的中央运算逻辑单元(CALU)。

2. 乘法区段

在TMS320F240 单芯片中央处理器的硬件结构中,有一个能在一

个指令周期时序内完成32 位乘法的16′16 位硬件乘法器及二个

相关缓存器,其功能如下:

(1)16 位暂时缓存器(TREG):可加载被乘数之空间。

(2)32 位乘积缓存器(PREG):可接收乘法运算结果之空间。

47

3. 中央运算逻辑区段

TMS320F240 芯片内部如同其它微处理器一样,有专门在做算数

运算及逻辑运算的地方,其即为中央运算逻辑单元。

(1)中央运算逻辑单元

执行算术及逻辑运算功能,且在一个频率周期内可完成。这些

功能可大致分为:加法、减法、逻辑运算及位的测试、位移、

旋转。

(2)累积器

为32 位结构,一般的数据存取都要透过累积器,而由于记

忆体的宽度多为16位的宽度所以我们可以将32位的累积

器视为高阶位(ACCH)及低阶位(ACCL),其接受中央运算

逻辑单元的输出数据,并利用进位位对数据内容执行位移位。

(3)输出数据倍率位移器

其功能为当累积器的高阶位要存入到指定的数据存储器

时,可以用此移位器来做数据的处理。

内存结构

在设计单芯片微处理机系统时,首先必须要了解该单芯片的硬件

架构,才能充分且适切地发挥单芯片的完全功能。单芯片硬件结构中

最重要的部分就当属于内存结构了。内存的大小、配置方式,往

往决定了该单芯片是否适用的主要因素。TMS320F240 控制芯片为了

增进执行速度,在芯片上设计有快速的Flash EEPROM来搭配内部或

外部内存的执行,使处理器在程序的执行上更快速更有效率。

1. 程序内存

在TMS320F240 中其程序内存即是存放程序本体的地方,由

MP/MC 此接脚信号可将其区分为使用微处理模式(Microprocessor)或

微电脑模式(Microcomputer),若使用微电脑模式则MP/MC 接脚应为

低电位,此时TMS320F240 使用内部程序内存,于TMS320F240

中,其内部具有Flash EEPROM可以烧录程序;而当使用微处理模式

时其MP/MC 接脚应为高电位,此时其芯片内部的程序内存将会被

禁能,微处理器就只执行外部内存内的程序。

2. 数据存储器

在TMS320F240 内的数据存储器有为每一个处理器单独使用的

内存,即所谓的区域性的数据存储器。另外当有多个处理器时,所

共享的数据存储器则称为共同区域数据存储器(Global Data

Memory),数据存储器主要是作为数据的存取以及作为外围控制、I/O

内存地址的映像内存,其根据状态缓存器理的数据页与地址来做

分页。

3. I/O 空间(I/O space)

在TMS320F240 内定义了64K 的I/O 空间,用来与外面的一些

装置做沟通用的,这些外围视场合而定可以是LED 灯、控制器,或

控制电路等,也是透过16 位的地址总线(A0~A15)、数据总线

(D0~D15),与外部的触发信号IS 来作为触发之动作。当使用这些指

令时,IS 的触发信号会变成低电位,使我们可以藉由对这些信号的解

码处理而来对外部的外围进行控制。

事件管理者模块

事件管理者模块提供广泛的功能及特性,主要功能如下:

(1)三组通用定时器(General Purpose timers,GP)。

(2)三组完全比较单元(Full Compare Units)。

(3)三组简易比较单元(Simple Compare Units)。

(4)脉波宽度调变(PWM)电路:包括空间向量PWM电路、停滞

带(dead-band)产生单元及输出逻辑。

(5)四组捕捉单元(Capture Units)及中断逻辑(Interrupt Logic)。

(6)方形编码器脉波 (Quadrature Encoder Pulse,QEP) 电路。

1. 比较单元

在事件管理者模块中总共有三组完全比较单元及三组简易比较

单元,每一组完全比较单元皆可工作在二种模式:比较模式与PWM

输出模式。完全比较单元的时间基底是由第一通用定时器提供,简易

比较单元的时间基底则是由第一或第二通用定时器提供。这些比较单

元的主要用途是作为脉宽调变的输出,通常在做脉宽调变时需要做一

些参数的设定,来决定所比较出来的脉宽是要何种型式并可由通用计

时器的设定来决定比较所需要的周期,以达到控制目的。

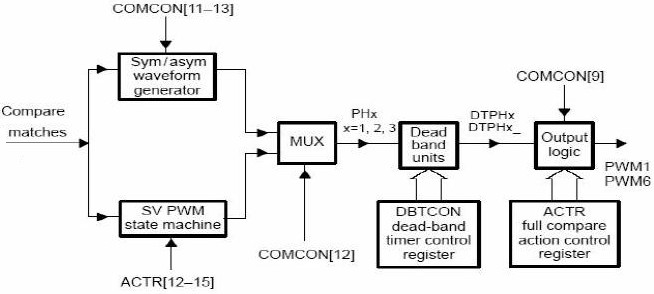

2. 脉波宽度调变(PWM)产生器

TMS320F240 拥有三组独立的脉波宽度调变产生器:完全比较/

脉波宽度调变产生器、简易比较/脉波宽度调变产生器及通用定时器

比较/脉波宽度调变产生器。每一组脉波宽度调变产生器皆可各别产

生三组独立之脉波宽度调变信号。其中,完全比较/脉波宽度调变产

生器可同时产生三组相依之脉波宽度调变信号,可符合本文之切换式

磁阻电动机之控制需求,故本文使用此三组完全比较/脉波宽度调变

产生器来驱动六颗功率开关组件。图2 为脉波宽度调变电路方块

图,包含下列几个单元:非对称/对称波形产生器、可程序停滞带单

元(Programmable Dead-Band Unit)、输出逻辑,及空间向量(Space

Vector)脉波宽度调变信号单元。其中非对称/对称波形的产生,可藉

由规划通用计数器为连续上数的模式或连续上/下数的模式而决定,

本系统所使用之非对称脉波宽度调变信号波形如图3 所示。为了产

生PWM信号,一组合适的定时器是必须的,它可以重复计数与PWM

周期一样的周期数。比较缓存器(CMPRx , x = 1,2,3)存有其调变值,

其值将不断与定时器之计数值(T1CNT)作比较,当比较符合时,相对

应之输出脚位将发生转态。为了要让脉宽调变信号的宽度达到所要求

的输出,需要设定下列的控制缓存器:

(1)通用定时器1 的周期缓存器(GP Timer 1 Period Register)。

(2)完全比较动作控制缓存器(ACTR)。

(3)比较控制缓存器(COMCON)。

(4)通用定时器1 控制缓存器(T1CON)。

(5)停滞带(dead-band)时间控制缓存器(DBTCON)。

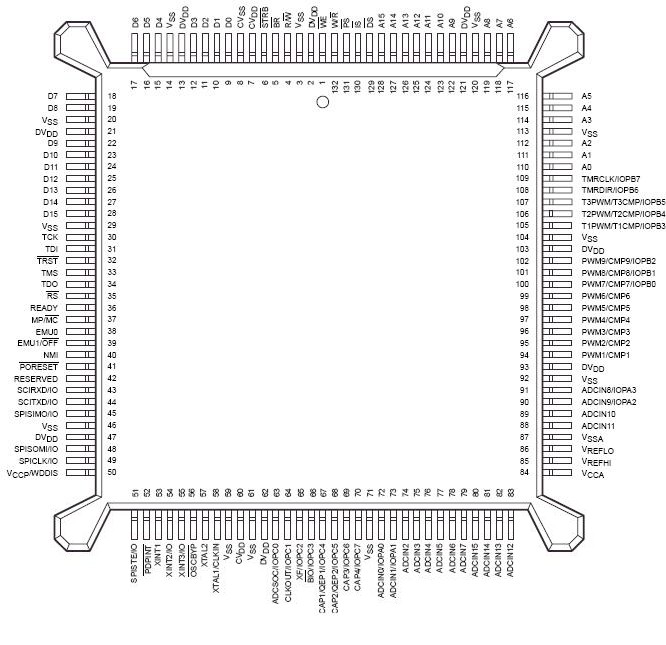

图1 引脚功能图 |

图2 脉波宽度调变电路方块图 |

图3 非对称脉波宽度调变信号波形

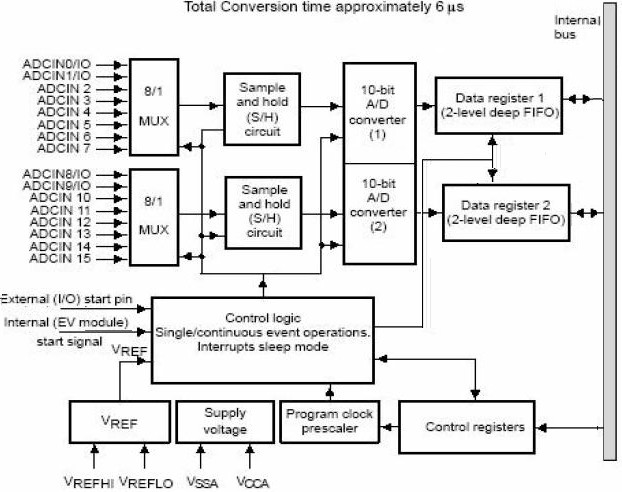

3. 模拟/数字转换器模块

模拟/数字转换器模块,为一个有内部取样保持器设计的10 位

转换器,图4 为模拟/数字转换器模块方块图。TMS320F240 内所提

供的模拟/数字转换器模块共有2 组,总计共有16个模拟输入通道

(Channel),而每8 个模拟输入信号藉由一组8对1的多任务器,选择

其中之一个信道进行模拟/数字转换的工作。每一个ADC 总转换时间

约为6μs,而ADC 的参考电压必须由外部电源供应(须低于+5V)。其

特性如下:

(1)每组ADC 有8 个模拟输入通道,合计共有16 个模拟输入。

(2)转换动作可采用单一转换(Single conversion)或连续转换

(Continuous conversion)方式操作。

(3)可由程序软件、内部事件或外部事件来启动转换。

(4)高参考电压(VREFHI)或低参考电压(VREFLO)输入。

(5)提供二层深的数字缓存器,用来储存转换完成后的数字值。

(6)提供二个可程序ADC 模块控制缓存器,可令两组ADC 独立工作。

(7)可选用可程序频率比率器(prescaler),调整其转换的时间,以

保持最佳之转换性能。

(8)可选用中断或轮询模式操作。

图4 模拟/数字转换器模组方块图 |

由于ADC 模块的内部结构,为了确保一个准确转换动作,转换

时间必须大于或等于5.5μs,而在任何系统频率频率可能设计在破坏

此关系下,因此在ADC 模块中,提供一个比率器(prescaler),以允许

当DSP 频率在应用上需要改变时,仍能维持最佳之转换性能。使用

者可选择ADC 比率器之内含值使得整个ADC 取样/转换时间可以大

于或等于5.5μs。此比率器(prescaler)之内含值必须满足下式:

系统频率周期(SYSCLK)×比率值×5.5≥5.5μs

评论

不錯