基于FPGA动态可重构技术的二模冗余MIPS处理器

引言

现场可编程门阵列(Field Programmable Gate Array,FPGA)是基于SRAM的一种硬件电路可重配置电子逻辑器件,可通过将硬件描述语言编译生成的硬件配置比特流编程到FPGA中,而使其硬件逻辑发生改变。FPGA在电子设计中的灵活性和通用性使其在航天、通信、医疗和工控等重要领域得到了广泛的应用。然而,FPGA中的硬件逻辑电路容易受到SEU(Single Event Upset)和SETs(Single Event Transients)故障的影响,从而导致系统失效。FPGA电路失效降低了基于FPGA的嵌入式系统的稳定性和寿命,同时会严重限制它在生产和生活各个方面的应用范围。系统备份、系统故障恢复和系统多模冗余设计是防止系统失效的有效方法。FPGA动态局部可重构技术是一种可应用于系统故障恢复的新兴技术,它可以在FPGA系统运行的过程中,动态地改变FPGA内部的部分逻辑电路块的逻辑功能,同时又不会影响其他逻辑的正常运转;二模冗余技术是一种典型的系统冗余容错设计方法,它为系统的重要模块设置备份模块,保证系统出现故障时依然可以稳定可靠地运转。基于上述思想,本文设计了一种基于FPGA动态可重构技术的二模冗余MIPS处理器。

1总体方案

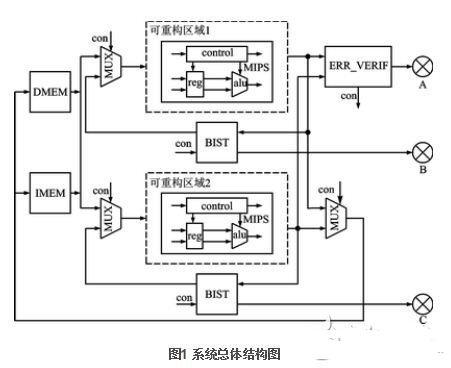

Xilinx公司的XC5VLX110T开发板是一个内含ML509芯片、具备内部逻辑块可动态配置能力的FPGA开发板。Verilog是一种结构化可综合的硬件描述语言,通过它可以很快地实现数字逻辑电路的结构级系统建模。本文以Xilinx公司的XC5VLX110T开发板作为系统开发平台,以Verilog语言开发了一种基于二模冗余结构的MIPS处理器系统。系统整体结构如图1所示。

系统的主要组成部分如表1所列。

IMEM是一个采用Xilinx公司IP生成器生成的FPGA内建存储器,由于MIPS处理器运行过程中不会改变指令存储器的内容,所以它被设计为无时钟门控的单端口只读存储器,存放MIPS处理器系统要执行的指令。IMEM的数据位宽为32位,存储深度为1 024.DMEM同样也是使用IP生成器生成的存储器,它存放MIPS处理器执行过程中所需的数据,是具有时钟边沿控制和使能控制的可读写单端口存储器。DMEM的数据位宽为32位,存储深度为1 024.MIPS模块是一个包含完整数据通路、ALU和控制逻辑的使用Verilog语言描述的单周期MIPS处理器,它的指令集大小为32,所有的指令均为整型操作指令。此处理器模块含有指令存储器和数据存储器外部接口,它是系统核心模块,所以被设计为FPGA中的可重构区域。ERR_VERIF模块是故障检测模块,它能对两MIPS系统的执行结果进行对比,并生成相应的故障控制信号;BIST模块也称为内建自测试模块,只有系统发生故障时,此模块才启动运行。它用来测试各子系统的正确性,并输出测试结果。

在图1中,以虚线框起来的部分为FPGA中的可重构区域。图中有两个可重构区域,上一个区域为主子系统区,下面一个区域为主子系统区的备份区。

2工作原理

系统上电复位后,在两MIPS内部逻辑均正常的情况下,系统执行过程为:指令存储器根据系统复位后的指令执行地址将指令从IMEM中取出,送入两个MIPS系统中;两个MIPS处理器分别在指令的指示下完成相应的工作,然后将执行结果输出到ERR_VERIF模块、DMEM和IMEM模块;ERR_VERIF模块分析系统是否正常运转,然后将分析结果信息输出到FPGA上的LED灯A上。

当其中一个MIPS处理器的内部逻辑发生故障时,可假定为图1中上方的主MIPS区域故障。系统执行过程为:ERR_VERIF故障检测模块检测到系统的子区域出现故障,然后发出故障位置检测控制信号;此时,BIST模块接收到检测控制信息后,启动内建自测试系统,将故障测试向量输入MIPS系统。在开启了BIST模块后,系统的指令输入将不再来自IMEM模块,而是由BIST模块提供。同时,指令的执行结果也不会写回到DMEM模块中,而是反馈到BIST模块中。MIPS根据测试向量进行运算,然后将运算结果反馈给BIST单元。BIST单元的测试要进行多次,以确保对故障的准确判断。BIST得到执行结果后,对测试结果进行分析并判定当前MIPS系统是否正常运行,最后分别将分析结果输出到FPGA上的LED灯B、C上。

ERR_VERIF模块的故障分析方法为比较法。它将执行同样指令且同步运行的两个子系统的执行结果进行比较,当发现结果不一致时,就表示其中一个子系统出现了故障,这时需要使用BIST模块去主动定位故障位置。而BIST进行故障分析的方法与ERR_VERIF模块使用的方法本质上是相同的,但是实现方式不同。BIST模块将被测试模块产生的输出与BIST内部存储好的预期的输出进行比较,来测试被测模块是否出现故障。

检测出的故障情况有3种:主子系统故障、备份子系统工作正常;主子系统正常、备份子系统故障;主系统子系统和备份子系统均出错。BIST模块检测出故障情况后,会将故障情况显示于故障灯(也就是A、B、C)上。当3个故障灯中有灯亮时,则表示系统出现故障。灯A、B亮,表示主子系统出现故障;灯A、C亮,表示备份子系统出现故障;灯A、B、C亮,表示两子系统均出现了故障。在出现故障后,系统会根据具体情况,对系统输出进行调整。当主子系统出现故障而备份子系统未出现故障时,系统输出则来自备份子系统;当备份子系统出现故障而主子系统未出现故障,系统输出则来自主子系统。当两子系统都出现了问题时,则需要停机维护。当其中一个子系统出现故障时,需要将无故障的子系统比特流重新下载入FPGA系统中。在下载时,系统的工作无需停止。

3内建自测试技术与BIST结构分析

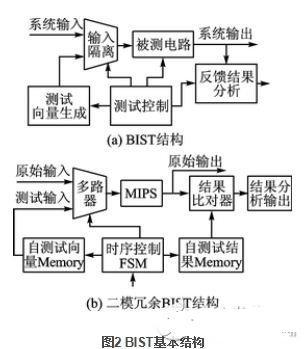

内建自测试技术(Build?in Self Test,BIST)是指在设计电路时,为了及时监测系统的状态,而设计一部分自测试电路来测试电路运行是否正常。BIST系统主要组成部分有测试向量生成、测试输入隔离、输出结果反馈分析和测试控制等,如图2(a)所示。

测试向量生成部分用于产生要输入到被测模块的测试向量,测试向量的生成含有两部分:测试输入的生成和测试结果的生成。测试输入用于作为被测电路的数据输入,而测试结果则用于对反馈结果的分析。测试输入隔离部分用于将BIST模块的测试向量输入和正常输入相分离。输出结果反馈分析部分用于分析被测电路中输出结果的正确性,并向外输出电路故障信息。

只用一组测试向量对电路故障进行测试将不具有可信度,所以在BIST技术中,通常需要使用多组测试向量对被测电路进行测试,因此在测试时需要一定的时序控制机制,测试控制部分用于完成测试的时序逻辑的控制。

图2(b)为系统中的BIST模块的详细结构图。其中“自测试向量Memory”和“自测试结果Memory”的功能相当于图2(a)中测试向量生成器的功能,“自测试向量Memory”用于存放测试输入向量,“自测试结果Memory”用于存放测试对比结果。而“时序控制FSM”用于对测试时序的控制,包括测试向量地址生成、测试结果地址生成和测试输入隔离控制等。“结果比对器”用于将MIPS实时输出结果与“自测试结果Memory”单元的输出结果进行比较。“结果分析输出”单元是一个状态机,将根据“结果比对器”的输入来进行状态转换。图3为具体的时序控制状态机。

4系统测试与分析

二模冗余系统的内建自测试中一共测试了6条指令。由于在实验中无法模拟出系统出现随机错误的情况,故测试时在电路中设置了一个人为出错的控制电路来产生系统故障。实验结果证明当二模系统出现故障时,BIST会自动启动去检测系统故障位置。当系统出现故障时,通过对出错部分的重新配置,可以使得系统恢复正常。

结语

本文根据FPGA动态部分重构技术、二模冗余技术,设计了一个基于二模冗余的MIPS处理器系统,系统可以对系统错误进行自行检测和错误自行定位,经测试系统可以正常运行。本系统下一步的工作是进一步完善故障自检测系统和设计故障的自修复系统。

评论