MIC2550引脚功能和内部结构

MIC2550引脚图

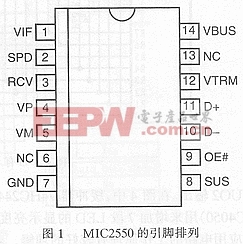

MIC2550通用串行总线收发器采用14脚双列贴片式TSSOP封装形式,它的引脚排列如图1所示。表1所列为各引脚的功能说明。

表1 MIC2550的引脚功能说明

引脚号 | 引脚名称 | 功 能 说 明 |

1 | VIF | 系统接口电路电源电压输入端。用于确定系统接口信号到逻辑控制器的逻辑电压电平 |

2 | SPD | 速率使能控制输入端。该脚为高电平时,器件选择全速率操作;该脚为低电平时,器件选择低速率操作 |

3 | RCV | 系统接口接收数据端。系统所要接收的数据通过该脚从逻辑控制器传输到系统接口上 |

4 | VP | 信号输入/输出正极接入端。在系统接口信号连接到逻辑控制器时,如果OE#为逻辑1,则VP端信号为接收器的正向输出;如果OE#为逻辑0,则VP端信号为驱动器的正向输入 |

5 | VM | 信号输入/输出负极接入端。在系统接口信号连接到逻辑控制器时,如果OE#为逻辑1,则VM端信号为接收器的负向输出;如果OE#为逻辑0,则VM端信号为驱动器的负向输入 |

6,13 | NC | 不用端口,通常悬空 |

7 | GND | 接地端口 |

8 | SUS | 功耗控制选择端。该脚为高电平时将关闭内部电路以减小电路的电源电流消耗 |

9 | OE# | 输出使能输入端。用于激活来自于逻辑控制器的系统接口输入信号。该脚为低电平时可使发射器向总线发射数据;为高时,则使接收器从总线上接收数据 |

10 | D- | USB数据串负端 |

11 | D+ | USB数据串正端 |

12 | VTRM | 终止电源输出端。在3.3V速率时,该端应外接一个终止电阻到电源输出 |

14 | VBUS | USB电源电压输入端。用来为收发器提供电源 |

评论