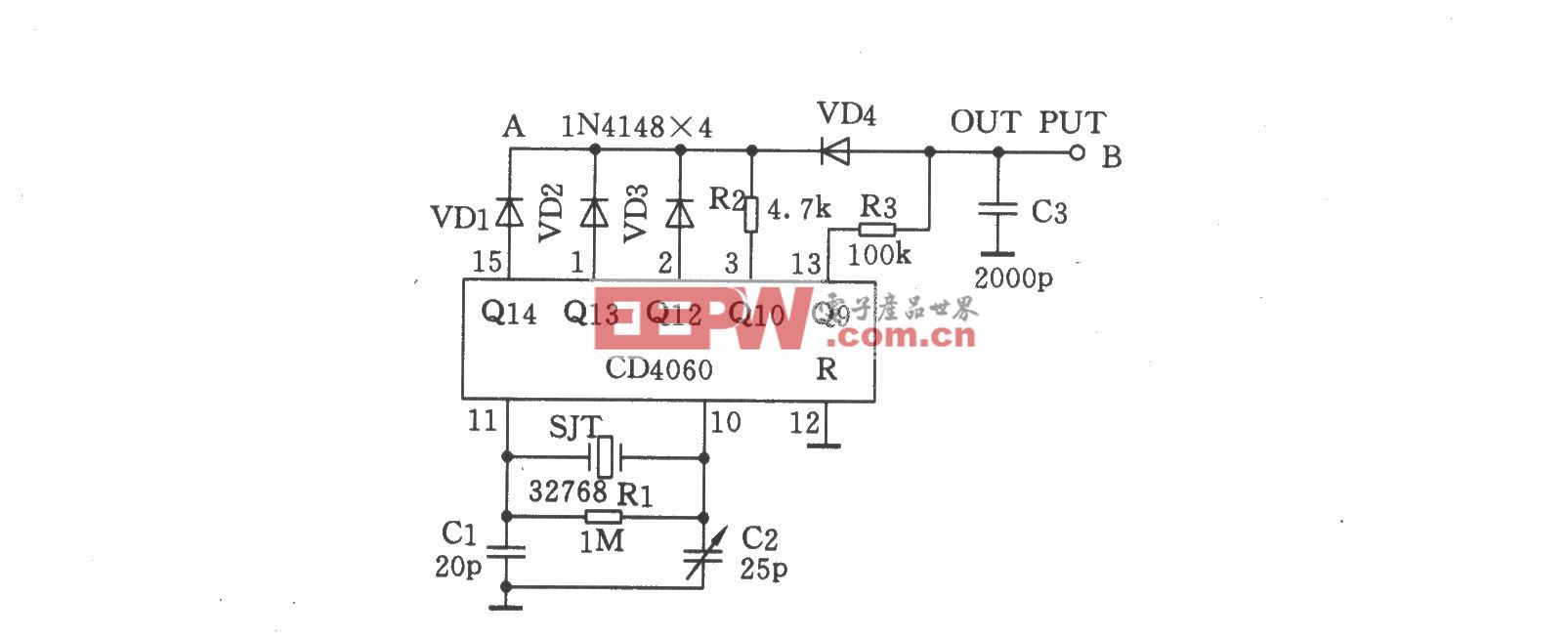

廉价高精度数字钟时基振荡电路

如图是利用一片价廉的CD4060和32768Hz晶体产生高精度每秒输出60个脉冲的时钟源。原理是32768Hz脉冲经CD4060分频后在15、1、2、3脚输出2Hz、4Hz、8Hz、32Hz脉冲,输入由VDl、VD2、VD3、R2组成的或门后,使A点每l/2秒中有1/32秒的低电平,封锁13脚输出的64Hz信号中的2个脉冲,这样就可每秒从13脚输出的64Hz脉冲中除去4个,在B点形成不规则的60Hz时基。C3的作用是消除13脚与A点竞争冒险而产生的极小脉冲。如无C3,B点输出将仍为60Hz。

评论