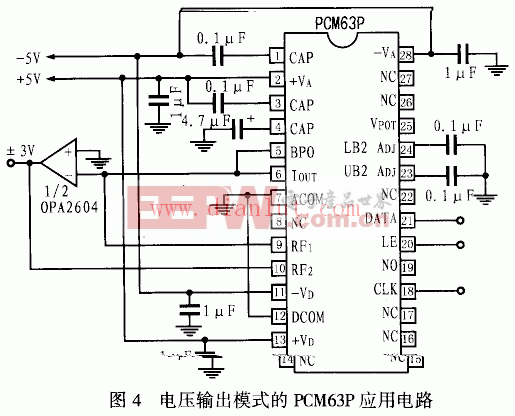

电压输出模式的PCM63P应用电路

下面是 [电压输出模式的PCM63P应用电路]的电路图

PCM63P的应用

PCM63P能够接收与TTL兼容的逻辑电平。在输入线上,采用差动电流模式的逻辑输入结构改善了PCM63P的抗噪声干扰能力。PCM63P的数据形式采用的是二进制补码形式,是最高有效位在前的串行数据流。位串中的任何数字都可以在20位数据前加载,因为在LE(寄存器使能信号)变低后,只有在它之前的最后20位数据才能转移到并行DAC寄存器中。

在PCM63P芯片中,DAC的串行数据输入位都在时钟CLK的上升沿触发,DAC的串行到并行数据的转换是在使能信号LE的下降沿进行的。其转换时序图如图3所示。PCM63P的典型时钟速率为16.9MHz。

(责任编辑:admin)

评论