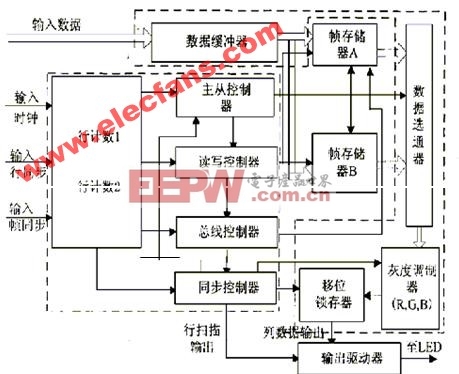

FPGA显示扫描框图

FPGA显示扫描框图

扫描控制模块

我们采用Altera公司的FPGA ACEX1K50中,主要完成扫描显示控制功能。它从帧存储器中读取要显示扫描显示的数据,然后按LED显示屏的逐行动态扫描格式产生控制时序。帧存储器中的数据,经MC93238MX处理后,写入到帧存储器,用于对显示屏的刷新。由地址产生器自动生成读地址信号完成对帧存储器内容的读出。在这过程中,要做好两个帧存储器的写地址和读地址、写数据和读数据的切换。读取后的数据在区计数器的作用下译码后被打进到相应的32位的区锁存器中,当所有区的数据均被锁完后,在统一的锁存控制信号作用下,同时将所有的区锁存器的数据锁进各自区的移位寄存器(32位并/串转换电路)中,然后由移位时钟Txd控制并完成移位操作实现数据的串行输出。同时由于显示屏的大小、颜色以及扫描方式可以有不同的组合,为了能在线配置以适合不同的显示平台,我们设计了颜色控制器(IO空间:0001H单元)、屏体高度控制器(IO空间:0002H单元)、扫描方式控制器(IO空间:0003H单元),它们在接收来自MC9328MX1的控制信息,然后根据这些信息控制地址计数器。其框图结构如图6所示:

评论