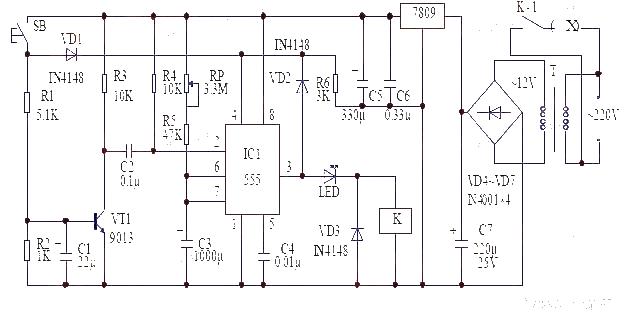

典型的抗干扰定时器电路图

典型的抗干扰定时器电路

如图为典型的抗干扰定时器电路图。该电路的原理:在SB断开时,555的4脚通过电阻器R6与地相连,555电路被强制复位。此时,无论2脚受到多大的干扰,555电路都不工作。当按下按钮B后,电源通过二极管VD1加到4脚一个高电平,时基电路的强制复位功能解除,同时电源通过电阻器R1加到三极管VT1的基极上,使得VT1导通,电容器C2通过与VT1集电极相连后向IC电路的2脚输出一个低电平,IC翻转置位,3脚输出高电平,发光二极管点亮、继电器K得电,触点K-1闭合,插座对外供电,同时3脚的高电平通过VD2向4脚输出一个高电平使得电路自锁。当暂态结束后,电路翻回稳态,3脚输出低电平,继电器K失电,触头K-1断开,电路恢复到初始状态。

评论