MAX V参考设计电路|CPLD应用电路

MAXV特性:静态功耗低至45µW,延长了电池使用寿命;数字PLL(DPLL),灵活的实现了需要频率相乘或者移相的设计;用户闪存和嵌入式闪存,为关键系统信息提供非易失存储器

MAXV典型应用范围:有线和无线;工业和军事;消费类;广播MAXV参考设计应用电路:

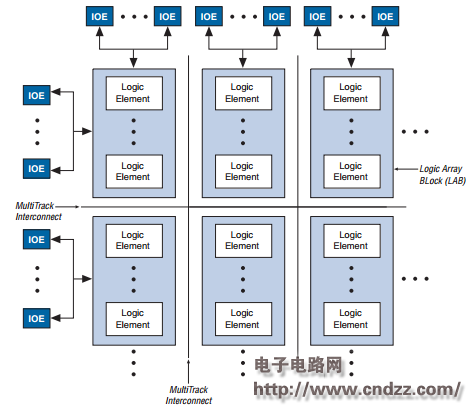

图1MAXV内部结构图

Each MAX V device contains a flash memory block within its floorplan. This block is located on the left side of the 5M40Z, 5M80Z, 5M160Z, and 5M240Z devices. On the 5M240Z (T144 package), 5M570Z, 5M1270Z, and 5M2210Z devices, the flash memory block is located on the bottom-left area of the device. The majority of this flash memory storage is partitioned as the dedicated configuration flash memory (CFM) block. The CFM block provides the non-volatile storage for all of the SRAM configuration information. The CFM automatically downloads and configures the logic and I/O at power-up, providing instant-on operation.

MAX V中文数据手册:点击下载

更多原理图及源代码热门应用电路:立刻点击

评论