ADC34J22 参考设计电路|数模转换器应用电路

ADC34J22属于高线性度、超低功耗、双通道、12 位、50MSPS 至 160MSPS 模数转换器 (ADC) 系列,此篇主要介绍了ADC34J22特性、应用范围、参考设计电路以及电路分析,帮助大家缩短设计时间。

ADC34J22 特性:

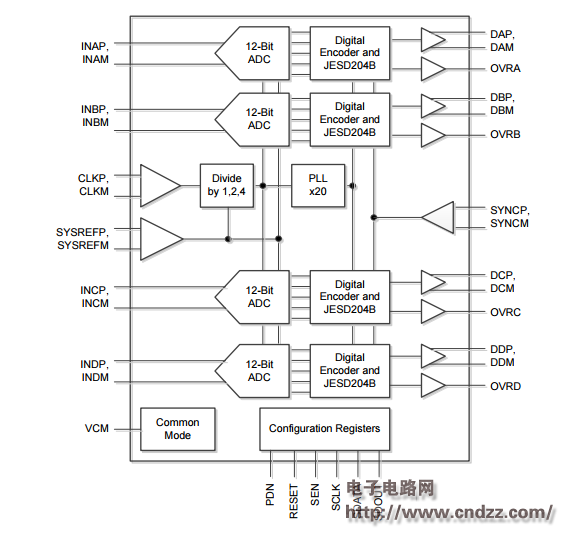

此类器件专门设计用于支持具有宽动态范围需求且要求苛刻的高输入频率信号。 当 SYSREF 输入实现整个系统同步时,时钟输入分频器将给予系统时钟架构设计更高的灵活性。 该器件支持 JESD204B 接口,从而减少接口线路的数量,实现高系统集成度。 JESD204B 接口是串行接口,仅通过一个差分对即可串行输出每个 ADC 的数据。 内部锁相环 (PLL) 会将传入的 ADC 采样时钟乘以 20,以获得串行输出各通道的 12 位数据时所使用的位时钟。 该器件支持子类 1,接口速率高达 3.2Gbps。

- 四通道

- 12 位分辨率

- 1.8V 单电源

- 支持 1 分频,2 分频和 4 分频的灵活输入时钟缓冲器

- 超低功耗:160MSPS 时为每通道 203mW

- 内部抖动

ADC34J22 典型应用范围包括:多载波、多模式蜂窝基站雷达和智能天线阵列、炮弹制导、电机控制反馈、网络和矢量分析器、通信测试设备、无损检测、微波接收器、软件定义无线电 (SDR)、正交和分集无线电接收器

ADC34J22 内部结构框图:

ADC34J22 参考设计电路:

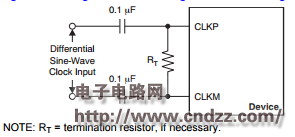

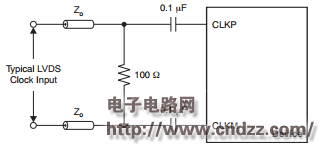

图1 Differential sine-wave clock Driving circuit 图2 LVDS clock driving circuit

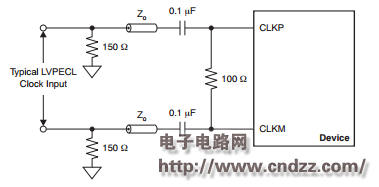

图3 LVPECL Clock Driving Circuit

ADC34J22 应用电路分析:The device clock inputs can be driven differentially (sine, LVPECL, or LVDS) or single-ended (LVCMOS), with little or no difference in performance between them. The common-mode voltage of the clock inputs is set to 1.4 V using internal 5-kΩ resistors. The self-bias clock inputs of the ADC34J2x can be driven by the transformercoupled, sine-wave clock source or by the ac-coupled, LVPECL and LVDS clock sources, as shown in Figure 1, Figure 2, and Figure 3.

ADC34J22 中文资料:点击下载

带有原理图和源码的热门应用电路请见:www.cirmall.com

评论