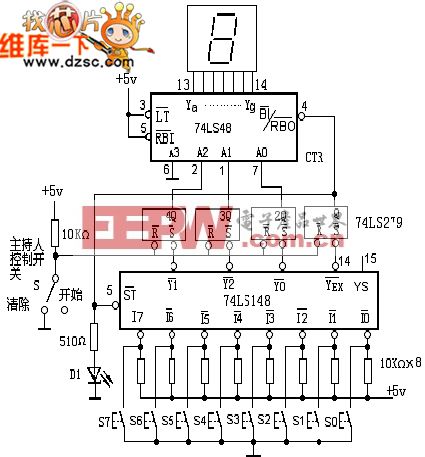

数字抢答器单元电路设计图

参考电路如图所示。该电路完成两个功能:一是分辨出选手按键的先后,并锁存优先抢答者的编号,同时译码显示电路显示编号;二是禁止其他选手按键操作无效。工作过程:开关S置于"清除"端时,RS触发器的 端均为0,4个触发器输出置0,使74LS148的 =0,使之处于工作状态。当开关S置于"开始"时,抢答器处于等待工作状态,当有选手将键按下时(如按下S5),74LS148的输出 经RS锁存后,1Q=1, =1,74LS48处于工作状态,4Q3Q2Q=101,经译码显示为"5"。此外,1Q=1,使74LS148 =1,处于禁止状态,封锁其他按键的输入。当按键松开即按下时,74LS148的 此时由于仍为1Q=1,使 =1,所以74LS148仍处于禁止状态,确保不会出二次按键时输入信号,保证了抢答者的优先性。如有再次抢答需由主持人将S开关重新置?quot;清除"然后再进行下一轮抢答。74LS148为8线-3线优先编码器,表11、1为其功能表。

评论

能不能写完整啊

GGGGGGGGGGGGGGGGGGGGGGGGG