5进制计数器设计方案汇总(三款计数器的电路原理图)

本文为大家带来三种5进制计数器设计方案。

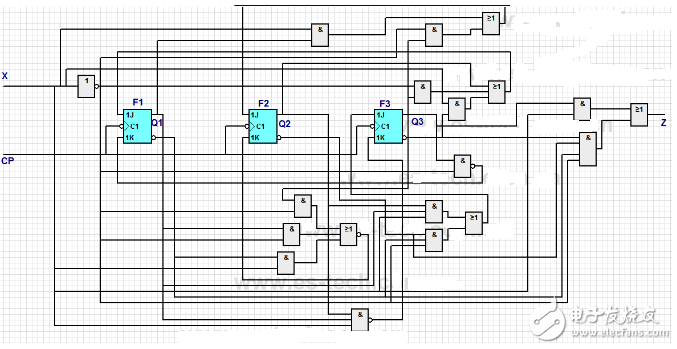

5进制计数器设计方案一:触发器组成的5进制计数器

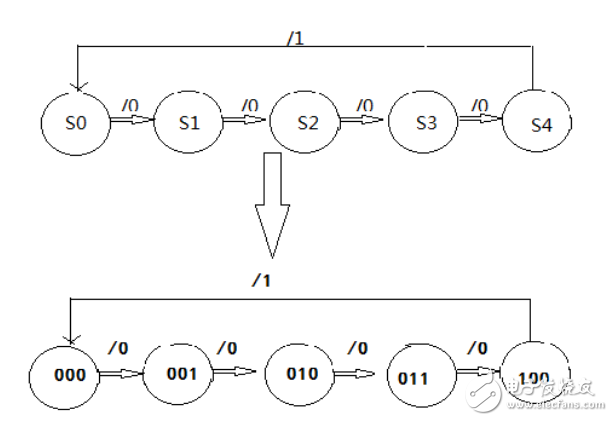

状态图

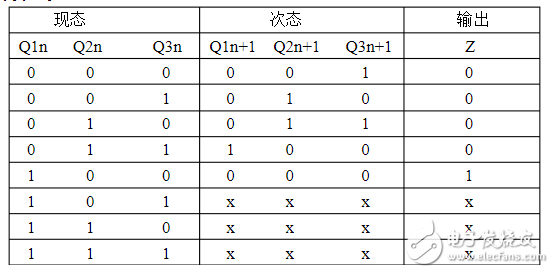

状态表

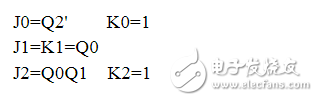

表达式

采用 JK 触发器,由状态表和触发器激励表可作出激励函数的卡诺图,根据卡图,得 J2、J1、J0,K2、K1.K0、Z 的表达式为

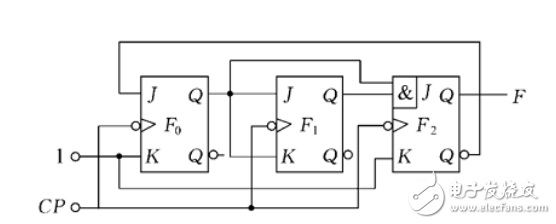

逻辑电路图

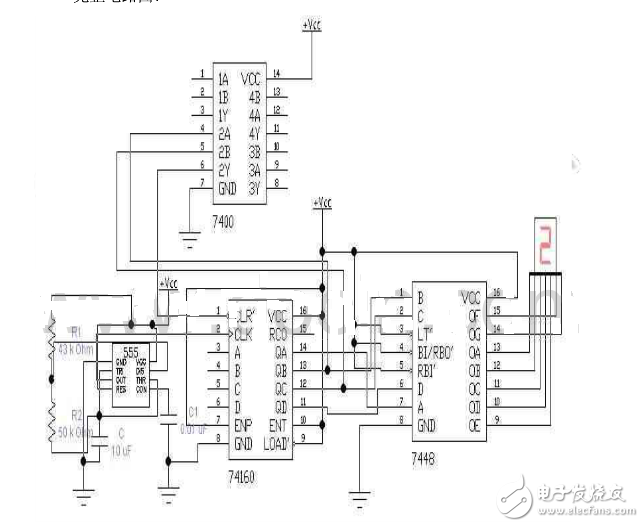

5进制计数器设计方案二:基于74ls160的5进制计数器设计

555 电路产生脉冲通过计数器74160进行计数,再经过译码器译码并由数码显示管显示具体的数字。在计数器和译码器之间用一个与非门7400 来控制数字显示的规律。

5进制计数器设计方案三:5进制加减法计数器设计

电路有三个无效状态:101,110,111。当电路进入任何一个无效状态后,当来一个脉冲,即有:Q3n+1=0,Q2n+1=1,Q1n+1=1,电路进入到状态S3=011,输出Z=0,由此可知该电路具有自启动能力。

评论