十路抢答器电路设计方案汇总(三款模拟+仿真设计电路图)

抢答器在各类智力竞赛之中经常出现,它的电路设计并不复杂,本文为大家带来三款十路抢答器电路设计方案。

十路抢答器电路设计方案一:用VHDL设计的十路抢答器

设计内容

(1)设计制作一个竞赛抢答器,共设10个组别每组控制一个抢答开关。

(2)设置主持人控制键,用于控制整个系统清零和抢答有效控制。

(3)主持人发出开始命令,10人开始抢答,其中一人先按下抢答键蜂鸣器会发出鸣叫,指示灯亮,数码管显示该人号码,其他人再按键,系统不再响应,直至主持人按键清零,下一次抢答开始。

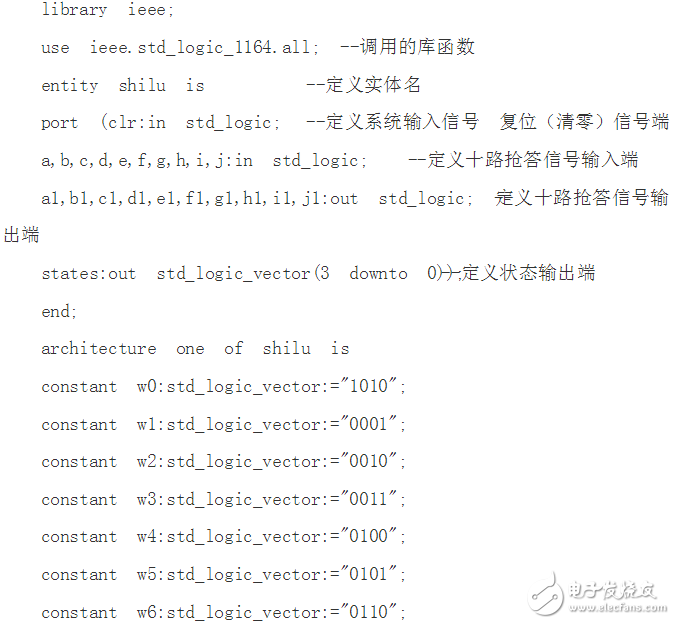

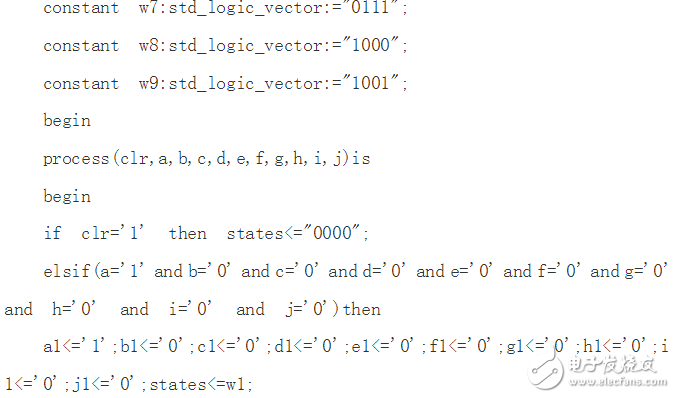

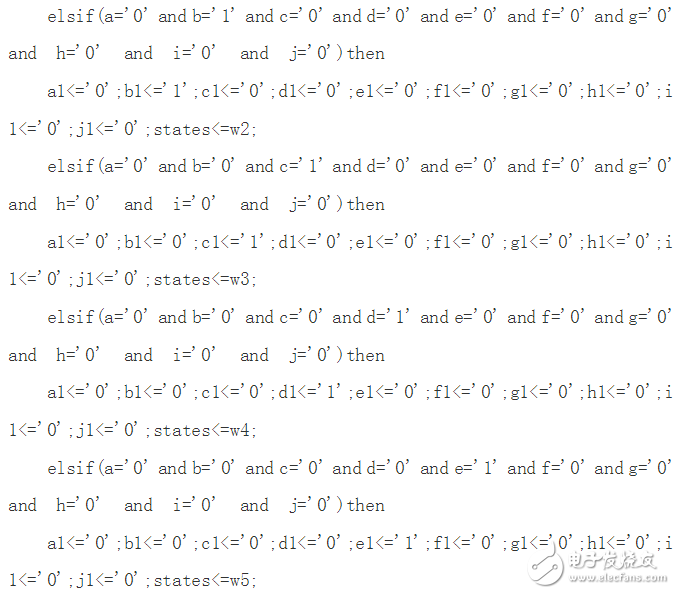

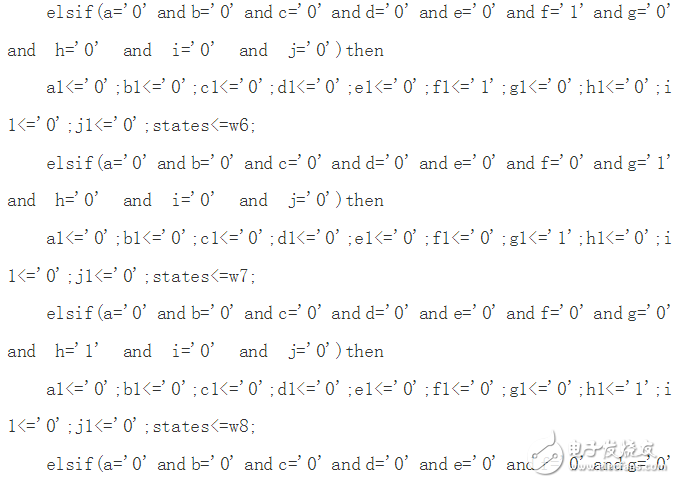

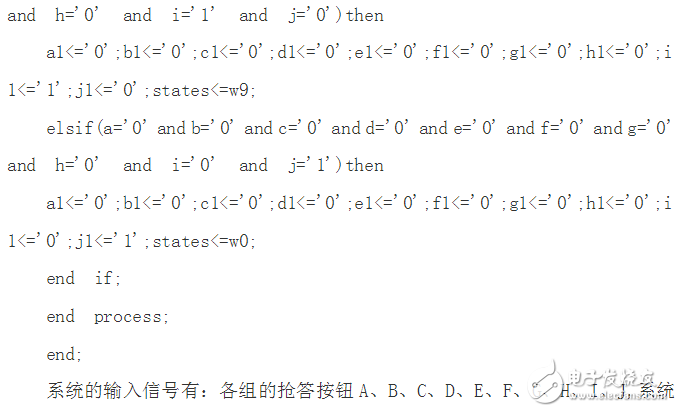

抢答鉴别部分程序

系统的输入信号有:各组的抢答按钮A、B、C、D、E、F、G、H、I、J,系统清零信号CLR。

系统的输出信号有:10个组抢答成功与否的指示灯控制信号输出口A1、B1、C1、D1、E1、F1、G1、H1、I1、J1作为控制蜂鸣器信号。

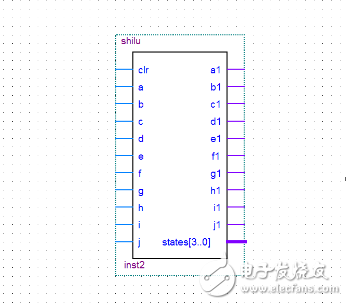

程序打包后如下图:

评论