74ls160设计数字秒表方案汇总(二款基于74ls160的数字秒表设计方案)

74ls160设计数字秒表方案汇总(一)

现场可编程门阵列(简称 FPGA)是20 世纪 80 年代中期出现的高密度可编程逻辑器件,采用SRAM开关元件的 FPGA 是易失性的,每次重新加电,FPGA 都要重新装入配置数据。突出优点是可反复编程,系统上电时,给 FPGA 加载不同的配置数据,即可令其完成不同的硬件功能。这种配置的改变甚至可以在系统的运行中进行,实现系统功能的动态重构。

“在系统可编程”(简称 ISP)是指对器件、电路或整个电子系统的逻辑功能可随时进行修改或重构的能力,支持 ISP 技术的可编程逻辑器件称为在系统可编程逻辑器件,它不需要专门的编程器,利用计算机接口和一根下载电缆就可以对器件编程了。

1、总体结构

本文利用 EDA 技术中的 Max + plus Ⅱ作为开发工具,设计了一款基于 FPGA 的数字式秒表 ,并下载到在系统可编程实验板的 EPF10K10LC84 - 4 器件中测试实现。其总体结构框架如图1 所示。图中的信号源是由实验板上的时钟信号经分频而得到的 0. 1 秒信号;控制计数部分由一个计数模块 ctrl 构成,用来实现计时功能,锁存器模块 latch 用来对数据进行锁存 ;而译码器模块 DISP 用来对计数结果进行扫描译码;数码管用来显示秒表的工作结果。

2、电路设计

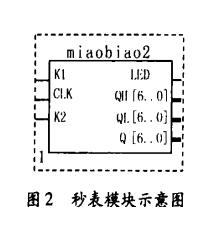

图2为数字式秒表的模块示意图。输入信号有三个,分别是 K1 , K2 和 CLK;输出信号有四个,分别是 LED ,QH[ 6. 。 0 ] ,QL[6. 。 0 ] 及 Q[ 6. 。 0 ]。其中 K1 为“开始/ 清零键”,接的是控制计数部分的整体清零端,该清零信号低电平有效。要求按下 K1 时计时开始 ,再按一下,停止计时,恢复到零状态。K2 为“固定显示键”,接的是锁存器 74373 的允许锁存端 G,该信号是高电平有效。在计时过程中,按下 K2 时,锁存数据 ,显示固定 ,但计时仍继续 ;按第二下时 ,显示从新时间开始。CLK 为时钟信号 ,必须是秒表计时所需的最小单位 0. 1S。

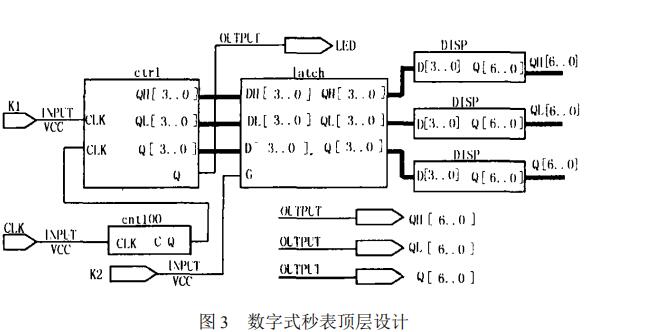

QH[6. 。 0 ] ,QL[6. 。 0 ] 及 Q[6. 。 0 ] 接三个数码管,分别表示秒十位,秒个位和秒十分位。LED 接发光二极管用来表示秒表的分位,当秒表计时超过59. 9 秒时 LED 灯亮,且能持续表示到 1分 59. 9 秒,然后灯灭,同时数码管重新计时显示,即该数字式秒表的计时范围从0 到2 分钟。基于原理图编辑和VHDL语言,并使用从上到下的设计方法设计的秒表,其具体的线路构成如图3 所示。

在总体电路图中,根据设计要求,输入信号 K1、K2 应采用脉冲开关。由于实验板上除了拨动开关就是瞬时的按键开关,且按键开关平时都呈高电平,按一下为低电平。故在实际测试时采用了拨动开关来模拟脉冲开关。根据设计要求将K1、K2 平时置于相应的高、低电平状态,需要清零或固定显示时再将它们分别置于相应的位置上即可。

3、模块设计

在设计电路时,要遵循从上到下的设计原则。首先从系统设计入手,在顶层进行功能划分和结构设计,顶层模块中的每个次层模块均可完成一个较为独立的功能,次模块在调试成功后可生成一个默认符号,以供上一层模块调用。

3. 1、时钟信号模块 cnt100

由于最终的设计结果要下载到可编程逻辑器件中测试,而承载该芯片的“在系统”可编程实验板上最小也是1 kHz 的时钟源,而秒表计时所需的最小单位为 0. 1s,故采用 2 片 74160,利用并行输入方式,接成 100 进制计数器(00~99),将 1 kHz 信号变成 10 Hz (即 0. 1 s),从而达到分频的目的。编译通过后创建的默认符号为 cnt100,其输入信号为 CLK,输出信号为 CQ(即高位的进位端 RCO) 。

3. 2、控制计时模块 ctrl

从 Maxplus2 器件库中调用 3 片 74160,采用串行时钟方式,连接成六百进制计数器(即 0~599),用来表示秒位。将 3 片 74160 的清零端 CLR 连接在一起,用来做秒表的整体清零端。再调用器件库中的 J K触发器,连接相应控制端形成 T′触发器,将六百进制计数器的进位信号接 T′触发器的时钟端。平时其输出端 Q 保持低电平,所接发光二极管不亮 ;当计时到 59. 9 秒时,由于有进位信号到来,因此时钟端出现脉冲下降沿,触发器翻转,Q 由低电平变为高电平,发光二极管点亮,表示已计时到 1 分钟。再计到 1分 59. 9 秒时,过 1 秒,灯灭,同时数码管重新计时显示。该控制模块为图 3 中 ctrl 模块。

3. 3、锁存器模块 latch

因为秒表设计中要求在计时过程中能随时固定显示时间,而计时仍然继续,所以要用到锁存器。在本例中适宜采用 CD4511 芯片,因为它集合了锁存、译码和驱动功能。但由于 Maxplus2 器件库中没有此类芯片,故以锁存器 74373 外加译码器 7447 (DISP) 代替。在设计时从器件库中调用 2 片 74373 (8 位锁存器), 将它们的 OEN 统统接低电平,允许数据输出。G端接一起,作为允许数据锁存端 (高电平有效) 。锁存器部分编译通过后创建的默认符号见图 3 中的 latch 模块,输入信号有四个,分别是 DH[ 3. 。 0 ] 、DL[3. 。 0 ] 、D[3. 。 0 ] 及 G,输出有三个,分别是 QH[3. 。 0 ] 、QL[3. 。 0 ]及 Q[3. 。 0 ] 。

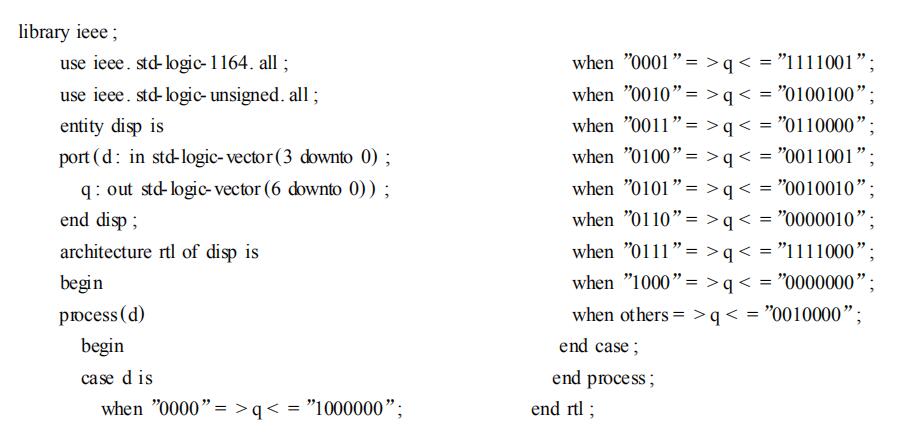

3. 4、译码显示模块 DISP

译码器可直接从器件库中调用 7447 (共阳极译码器),将它的控制端按要求接好,形成默认符号 ;也可用 VHDL 语言编程,将 4 位 BCD 码译成 7 段数码管的编码(0~9),现采用 VHDL 语言编程,编译无误后创建默认文件符号 DISP 以供上层电路调用。显示部分直接采用实验板上的 3 个共阳极数码管,不用将译码器的输出 a~g 具体连线到实验板上数码管的 7 个段,只需将其输出端口定义到可用作数码管显示的器件的 I/ O 引脚上即可。7 段数码管译码器源程序如下

4、编程及测试

为设计项目选定 FLEX10K系列中的 EPF10K10LC84 - 4 器件,锁定顶层设计中各端口所对应的引脚号,并编译通过。然后对器件编程,使用 ByteBlaste 下载电缆把项目以在线配置的方式下载到 ISP 实验板的 EPF10K10LC84 - 4 器件中,按相应的 K1、K2 键,观测数码管及发光二极管的状态,发现显示结果正确。该数字式秒表具有清零功能,能够在计时过程中随时停止计时,恢复到初始状态。且具有锁存/ 计时功能,能在计时过程中通过按“固定显示键”,将显示固定住,而计时仍继续 ;再按下键,显示从新时间开始。实验证明该秒表工作正常,基本上已达到了预期的设计要求。

5、结束语

在Max + plus Ⅱ开发环境下,采用自顶向下的设计方法有利于在早期发现结构设计中的错误,避免不必要的重复设计。再结合基于 FPGA 的“在系统”可编程实验板,轻轻松松就能实现各种电子产品的设计,现场观察实验测试结果。大大缩短了产品的设计周期和调试周期,提高了设计的可靠性和成功率,充分体现了可编程逻辑器件在数字电路设计中的优越性。

评论