JK触发器原理

边沿J K触发器

1 边沿JK触发器的结构与原理

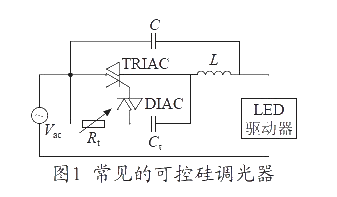

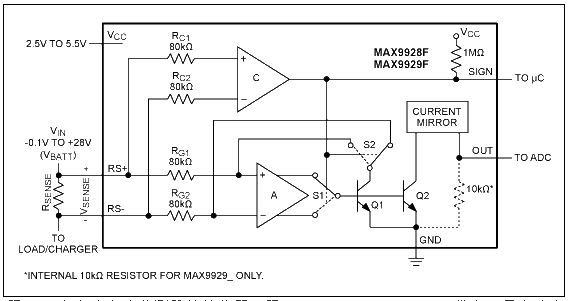

这种边沿触发器是利用门电路的传输延迟时间实现边沿触发的,电路结构如图1所示。

这个电路包含一个由与或非门G1和G2组成的基本RS触发器和两个输入控制G3和G4。而且,门 G3和G4的传输时间大于基本RS触发器的翻转时间。

设触发器的初始状态为Q = 0 、Q = 1 。 CP = 0时门B、 、G3和G4同时被CP的低电平封锁。而由于G3和G4的输出 P、

、G3和G4同时被CP的低电平封锁。而由于G3和G4的输出 P、 两端为高电平,门 A、

两端为高电平,门 A、 是打开的,故基本RS触发器的状态通过 A、

是打开的,故基本RS触发器的状态通过 A、 得以保持。

得以保持。

图1 边沿JK触发器

CP变为高电平以后,门B、 首先解除封锁,基本RS触发器可以通过B、

首先解除封锁,基本RS触发器可以通过B、 继续保持原状态不变。此时输入为J=1 、K=0 ,则通过门G3和G4的传输延迟时间后P=0、

继续保持原状态不变。此时输入为J=1 、K=0 ,则通过门G3和G4的传输延迟时间后P=0、 ,门A、

,门A、 均不导通,对基本RS触发器的状态没有影响。

均不导通,对基本RS触发器的状态没有影响。

当CP下降沿到达时,门B、 立即被封锁,但由于门G3和G4存在传输延迟时间,所以P、

立即被封锁,但由于门G3和G4存在传输延迟时间,所以P、 的电平不会马上改变。因此,在瞬间出现A 、B各有一个输入端为低电平的状态,使

的电平不会马上改变。因此,在瞬间出现A 、B各有一个输入端为低电平的状态,使 ,并经过

,并经过  使Q = 0 。由于G3的传输延迟时间足够长,可以保证在P点的低电平消失之前 Q 的低电平已反馈到了门A ,所以在P点的低电平消失以后触发器获得的1状态将保持下去。

使Q = 0 。由于G3的传输延迟时间足够长,可以保证在P点的低电平消失之前 Q 的低电平已反馈到了门A ,所以在P点的低电平消失以后触发器获得的1状态将保持下去。

经过G3和G4的传输延迟时间后, P 和![]() 都变为高电平,但对基本RS触发器的状态并无影响。同时,CP的低电平已将门G3和G4封锁,J、K状态即使再发生变化也不会影响触发器的状态了。

都变为高电平,但对基本RS触发器的状态并无影响。同时,CP的低电平已将门G3和G4封锁,J、K状态即使再发生变化也不会影响触发器的状态了。

2 特征表和特征方程

触发器稳定状态下J、K、![]() 、

、 之间的逻辑关系如特征表所示。

之间的逻辑关系如特征表所示。

| J | K | Qn | Qn+1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

特征表

由特征表可得出特征方程:Qn+1 = JQn + KQn

3 状态转换图和时序图

边沿JK触发器的状态转换图和时序图如图2所示。图(a)为状态转换图,图(b)为时序图,边沿JK触发器在给定输入信号J、K和CP的作用下,Q1端输出为触发器时钟的动作沿是上升沿和Q2端输出为下降沿的波形。

(a) (b)

图2 边沿JK触发器的状态转换图时序图

4,逻辑符号

边沿JK触发器分上升边沿和下降边沿两种,它的逻辑符号如图3所示,CP端有

空心圆符号的是下降边沿,无空心圆符号的是上升边沿。

(a) 上升边沿 (b) 下降边沿

图3 边沿JK触发器的逻辑符号

5 集成边沿JK触发器

(1).TTL集成边沿JK触发器

图4.21(a)是TTL集成边沿JK触发器74LS112引出端功能图。

(2).CMOS集成边沿JK触发器

图4 (b)是CMOS集成边沿JK触发器CC4027引出端功能图。

(a) (b)

图4 (a) 74LS112引出端功能图 (b) CC4027引出端功能图

评论

ggggggggggggggggggggggggg