d触发器原理

维持阻塞D触发器

1 维持阻塞D触发器的电路结构

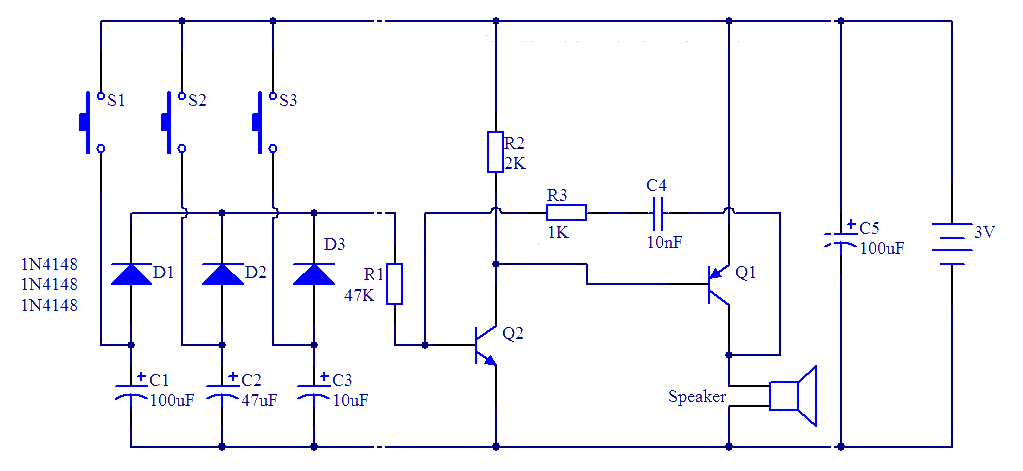

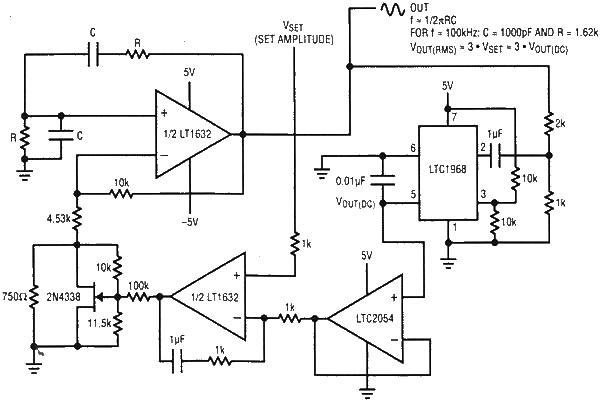

维持阻塞D触发器的电路如图1所示。从电路的结构可以看出,它是在基本RS触发器的基础之上增加了四个逻辑门而构成的,C门的输出是基本RS触发器的置“0”通道,D门的输出是基本RS触发器的置“1”通道。C门和D门可以在控制时钟控制下,决定数据[D]是否能传输到基本RS触发器的输入端。E门将数据[D]以反变量形式送到C门的输入端,再经过F门将数据[D]以原变量形式送到D门的输入端。使数据[D]等待时钟到来后,通过C门D门,以实现置“0”或置“1”。

图1 维持阻塞D触发器 图2 触发器置“1”状态 图3 触发器置“0”状态

2 维持阻塞D触发器的工作原理

D触发器具有置“0”和置“1”的功能。

设Q=0、[D]=1,当CP来到后,触发器将置“1”,触发器各点的逻辑电平如图2所示。在执行置“1”操作时,C门输出高电平;D门输出低电平,此时应保证置“1”和禁止置“0”。为此,将D=0通过①线加到C门的输入端,保证C=1,从而禁止置“0”。同时D=0通过②线加到F门的输入端,保证F=1,与CP=1共同保证D=0,从而维持置“1”,。置“0”过程与此类似。设Q=1、[D]=0,当CP来到后,触发器将置“0”。在执行置“0”操作时,C门输出低电平,此时应保证置“0”和禁止置“1”。为此,将C=0通过④线加到E门的输入端,保证E=1,从而保证C=0,维持置“0”。同时E=1通过③线加到F门的输入端,保证F=0,从而使D=1,禁止置“1”。以上过程见图1。

电路图中的②线或④线都是分别加在置“1”通道或置“0”通道的同一侧,起到维持置“1”或维持置“0”的作用;①线和③线都是加在另一侧通道上,起阻塞置“0”或置“1”作用。所以①线称为置“0”阻塞线,②线是置“1”维持线,③线称为置“1”阻塞线,④线是置“0”维持线。从电路结构上看,加于置“1”通道或置“0”通道同侧的是维持线,加到另一侧的是阻塞线,只要把电路的结构搞清楚,采用正确的分析方法,就不难理解电路的工作原理。

根据对工作原理的分析,可以看出,维持阻塞D触发器是在时钟上升沿来到时开始翻转的。我们称使触发器发生翻转的时钟边沿为动作沿。

图4是带有异步清零和预置端的完整的维持阻塞D触发器的电路图。这个触发器的直接置“0”和直接置“1”功能无论是在时钟的低电平期间,还是在时钟的高电平期间都可以正确执行。 图5 是D触发器的逻辑符号,从图5(a) 可看出CP是上升沿有效,当然,D触发器还有CP下降沿有效的,如图5(b)所示。

(a) (b)

图4 维持阻塞D触发器 图5 维持阻塞D触发器逻辑符号

3特征表和特征方程

表4.3为D触发器的特征表,特征表就是Qn将也作为真值表的输入变量,而Qn + 1为输出,此时的真值表称为特征表。有特征表可得特征方程:Qn+1=D

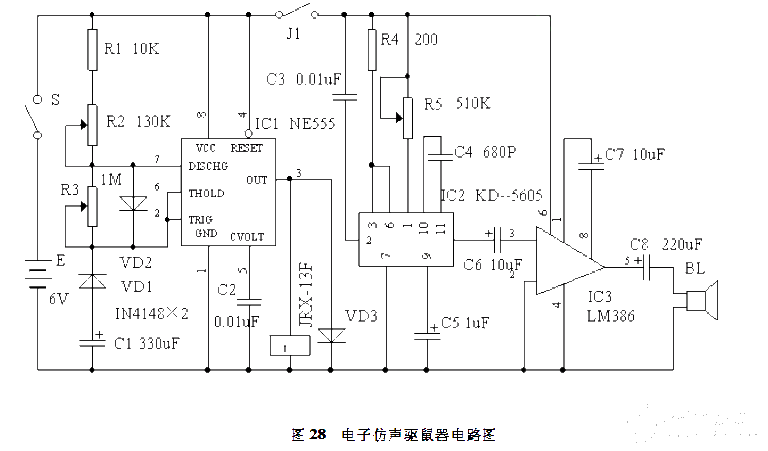

4 状态转换图和时序图

维持阻塞D触发器的状态转换图如图6所示, 图(a)为状态转换图,图(b)为时序图。

(a) (b)

图6 D触发器的状态转换图和时序图

5 边沿集成D触发器

1.TTL集成D触发器

图7所示是TTL边沿D触发器7474的引出端功能图。7474中集成了两个触发器单元,他们都是CP上升沿触发的边沿D触发器,异步输入端Rd、Sd低电平有效。

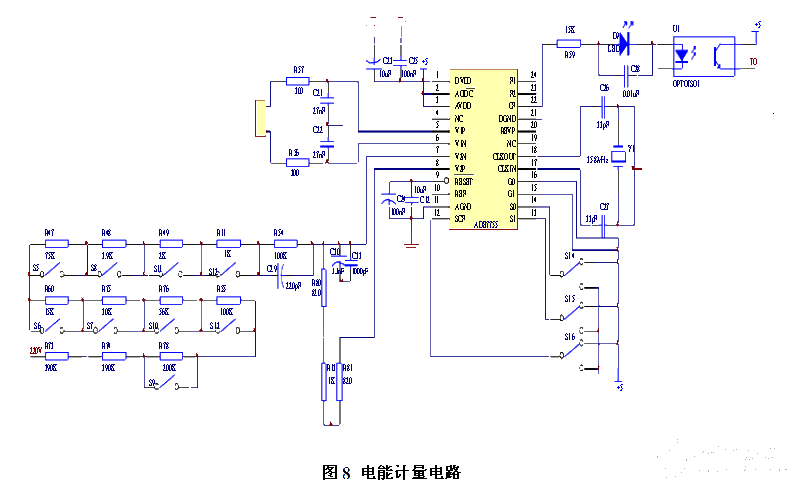

2.CMOS集成D触发器

图8所示是CMOS边沿D触发器CC4013的引出端功能图。CC4013中集成了两个触发器单元,他们都是CP上升沿触发的边沿D触发器,异步输入端Rd、Sd高电平有效,即Rd = 1触发器复位到0,Sd = 1触发器置位到1。

图7 7474的引出端功能图 图8 CC4013的引出端功能图

评论