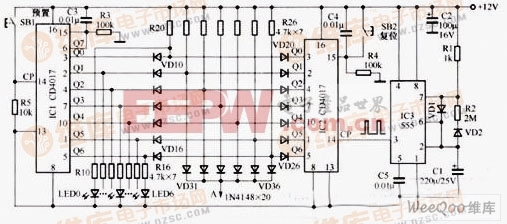

可预设数字式定时器电路图

可预设数字式定时器电路

如图IC3 与Rl 、R2 、Cl 及VDl 、VD2 共同组成一个超低频的脉冲振荡器。十进制计数/分频器CD40l7 将时基脉冲振荡器输入的时基脉冲进行分频,它有10 个输出端,本电路用到其中的7个。上电后IC2 的QO 首先输出高电平,当第一个时基脉冲输入后,Ql 输出高电平。此后,每当输入一个时基脉冲,lC2 的输出前移一位,定时时间增加5 分钟,直至Q6 输出高电平为止。ICl 组成于动式数字调整预置电路,当按动预置按钮SBl 一次后,就有一个计数脉冲输人计数器ICI,它的输出端就前移一位,最大移位数为6 位,每一挡位为5 分钟,最长预置时间为30 分钟。VDlO~VD16 组-成预置电路的控制门, VD20~VD26 组成时基分频输出的控制门, VD3l~VD36 组成提示音响信号输出的控制门。

该电路可以通过改变Rl 、R2 或Cl 的数值,改变时基脉冲的长度,从而改变定时时间。也可以将ICl 、IC2 的10 个输出端全部利用并增加相应的隔离二极管,扩大定时电路的调节范围。

评论