高性能信号处理通用平台研究

0引言

当前信号处理领域内阵列信号处理技术正在迅速发展,各种新的算法及新的处理技术不断出现,要求信号处理系统具有快速适应各种新算法和新技术的能力,采用传统的基于专用硬件的设计方法所开发出来的信号处理系统无法满足这样的要求。开发具有通用性的计算平台,尽可能通过软件来实现信号处理功能,成为信号处理的新趋势,“软件雷达”、“软件无线电”等概念都是基于这一思想。

通过灵活的软件编程来适应算法的变化,通过简单的硬件扩展来适应规模的变化,使系统的灵活性大大提高,研制周期、费用大为减少。要支持这种设计思路,必须研制出组成通用计算平台的信号处理模块,该模块既能满足系统实时处理需求,又具备通用性、可扩展性。

本文提出了一种基于TMS320C6701信号处理器的高性能信号处理模块的设计方案,设计了具有一定通用性的并行信号处理模块,该模块具有高速互连接口,可以根据应用系统的需求构成不同的并行系统,完成各种信号处理任务。

1系统结构

随着微电子技术的突飞猛进,处理器的速度不断得以提高,但实际应用对于计算能力的需求还是远远超出了单个处理器可以提供的范围,采用并行处理技术构成多处理器系统满足需要较强计算能力的应用是一种行之有效的技术途径。

并行处理的目的是通过采用多个处理单元同时对任务进行处理,加速整个计算的过程,从而减少任务的执行时间。整个任务可分解成一些小的任务,分别分配给并行处理系统中各个处理单元执行。一般而言,这些并行执行的任务都不能完全独立执行,一个任务中的计算可能需要用到另一个任务中的数据,各处理单元之间存在进行数据交换的要求。因为交换数据而必须等待的时间,反映了处理单元之间的同步开销。因此不难看出,并行处理额外增加了数据通信和同步等待等开销。

为使任务执行时间减少增加处理单元个数成为首要手段,同时要将任务进行更细粒度的划分以增加任务的并行度,但在增加处理单元和任务细粒度化的同时将带来总通信量的增加,再加上同步时间和任务分配不均所造成的空等待时间开销,增加处理单元的个数对增加系统处理能力得不偿失。这使得在设计并行处理系统时必须着重考虑以下两个方面:处理单元性能的提高以及处理单元间通信技术的改进。

1.1处理单元的选择

在通信、语音、图像处理中信号的动态范围有限,一般采用定点运算就可以满足要求,雷达、声纳信号需要较大的数据动态范围和数据精度,若按定点处理会发生数据上溢出或下溢出,严重时处理将无法进行,如果使用移位定标或用定点模拟浮点运算,程序的执行速度将大大降低,为增强计算平台的适用性,该通用信号处理平台使用浮点处理器。

同样的任务量,用高性能的处理单元构成的“小”规模系统,其效率要高于用较低性能的处理单元构成的“大”规模系统。并行处理单元的性能相当重要,它不仅包括运算速度,还包括存储器带宽、数据通信速度等,美国TI公司的TMS320C6000系列DSP是业界最高性能的通用可编程DSP,TMS320C6701又是该系列中性能较高的浮点处理器。该款DSP完全满足设计的通用计算平台对信号处理单元性能的要求,因此选择TMS320C6701作为信号处理模块的处理单元。

1.2通信网络的设计

阵列信号处理必然是多个信号处理单元并行工作,子任务分配在并行处理系统的各个处理单元中,子任务间数据通信速度和同步时间等不仅取决于处理单元本身的通信速度,还取决于连接处理单元的通信互连网络,通信链路丰富的复杂网络往往能提供较高的数据通信速度,然而其设计和维护的难度要高得多。针对不同的实际应用,采用不同形式的通信网络,可以降低通信网络的复杂度。

在互连结构设计中,把整个并行信号处理系统的互连结构分为两级:系统级互连结构、模块级互连结构。

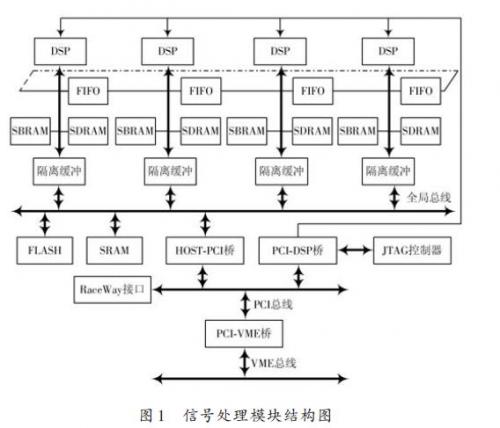

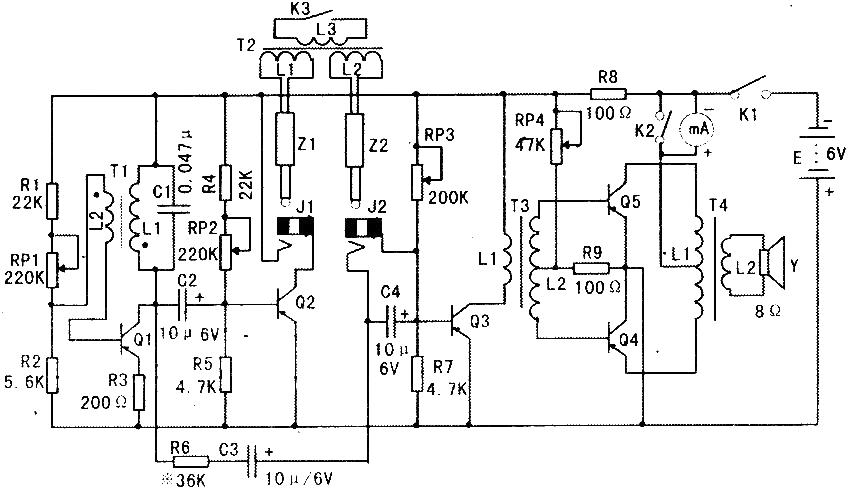

系统级互连结构主要用于模块间的通信,该设计中系统级的控制网络和信号处理网络分别采用RaceWay及VME实现。模块级互连结构主要指信号处理模块内的网络结构。信号处理模块系统结构如图1所示。

信号处理模块内包含4个DSP,可提供4GFLOPS的峰值处理能力。模块内采用共享总线互连结构。一般情况下,程序代码和运算数据应存放于各DSP的片内RAM或局部存储器中,这样可以减少共享存储器访问次数,减少总线争用,缩短存储访问延时。共享存储器通常用来支持模块内4个DSP之间交换数据,以及用来支持在模块之间交换数据。

为了减少模块内各个DSP争用总线带来的时延,提高DSP之间的通信能力,相邻的DSP之间还通过双向的FIFO连接,构成FIFO环。这种结构十分适合流水处理的应用,最大限度地减小了数据移动的开销,提高了处理器间的通信速度。

流水处理以其简单高效而被广泛采用,但因为它只利用了任务时间上的并行性,而忽视了空间上的并行性,所以并行度不高,加速比受到限制。当流水线中某一段任务负载量大于其他段时,就会形成处理瓶颈而降低系统效率。因此,流水线往往和并发操作结合起来,即在流水线处理的基础上,部分的利用空间并行性,称为局部并行全局串行网络。与之对应的是全局并行局部串行网络,即先利用空间并行性再利用时间并行性,设计出并行工作的多条流水线。

该并行信号处理系统的信号处理模块所采用的互连形式——共享总线和FIFO环的结构,能够很好地适应流水处理的各种变形。

2硬件设计

该信号处理模块符合VME标准,采用6U双高板结构,模块内部硬件实现上可划分为四级总线结构,分别是局部总线、全局总线、PCI总线以及VME总线。在局部总线上的资源有:SBRAM、SDRAM及双向FIFO;全局总线上的资源有:PCI总线接口、SRAM、FLASH;PCI总线上的资源有:RaceWay接口、HOST PCI的桥、PCI VME的桥以及PCI DSP的桥;VME总线上的资源有:

VME总线接口。

2.1存储系统设计

信号处理模块的存储器空间包括:局部总线空间和全局总线空间。局部总线空间由局部控制寄存器空间、SBSRAM空间、SDRAM空间、FIFO空间、内部程序存储器空间、内部数据存储器空间和内部外设空间构成。全局总线空间由全局FLASH空间、全局SRAM空间、全局总线控制寄存器空间和PCI接口空间构成。

EMIF是外部存储器和TMS320C6701片内各功能单元的接口,DSP访问片外存储器时必须通过EMIF.

EMIF具有很强的接口能力,其数据总线宽度为32b,可寻址空间为4GB,可以与目前几乎所有类型的存储器直接接口,数据吞吐能力最高可达667MB/s.EMIF支持的器件类型包括:同步突发静态RAM(SBSRAM)、同步动态RAM(SDRAM)、异步器件(包括异步SRAM、ROM和FLASH等),异步接口速度、时序可编程,可以配合不同的器件。

EMIF处理的外总线请求有四种来源:片内程序存储器控制器发出的取指请求,片内数据存储器控制器发出的数据存取请求,片内DMA控制器的请求,外部共享存储器设备的控制器发出的请求。当同时有多个部分申请外总线时,由EMIF根据设置的优先级进行仲裁,然后响应各个申请。一旦某个申请者根据优先级获得了处理权,这一处理权会一直保留到该申请者放弃请求或者是有更高优先级的申请者提出申请,其间即便有新的申请出现,EMIF也不会受理。在新的申请开始得到处理之前,对于已经获得处理权的前一个申请者,其尚未完成的操作部分可以优先继续完成。

2.2全局总线设计

模块内全局总线可由4个DSP、PCI接口芯片中的任何一个来占用,全局总线仲裁电路的设计是该模块设计中的一个要点。考虑到PCI接口是整个系统信息交换最重要的通道,它的利用率的高低直接决定了系统的性能,所以将其优先权定为高,将DSP的优先权定为低。DSP之间的仲裁采用轮转优先级仲裁算法。

DSP通过异步接口空间访问全局总线,由于TMS320C6701的异步接口空间仅能够提供4MB的地址空间,为了克服芯片的这个限制,采用页面的机制扩充异步接口空间,使该空间最大可访问的空间达到2GB.把DSP的EMIF提供4MB的异步接口空间分为两部分,低2MB(即A21=0)用于访问全局资源,高2MB用于访问每个DSP的局部资源。采用这种DSP异步接口空间的划分方法简化并加快了译码。当复位时每个DSP的页面寄存器都被置为0×0000 0000,它会自动通过异步接口空间指向FLASH,实现自举。当一个DSP获得全局总线的访问权后,由该DSP的页面寄存器决定全局总线地址的高11位(GA31:GA21),全局总线地址的低位(GA20:GA2)直接由该DSP驱动,GA1和GA0由译码得到。

通过以下计算公式可以计算页面值和页内偏移量:

页面值=(全局总线上的地址)

2.3调试接口

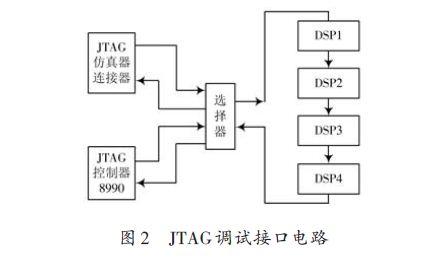

JTAG是基于IEEE 1149.1标准的一种边界扫描测试方式。TI公司为C6000系列DSP提供了JTAG端口支持,结合配套的仿真软件可以访问DSP的所有资源,包括片内寄存器以及所有的存储器,从而提供了一个实时的硬件仿真与调试环境,便于开发人员进行系统软件调试。

该信号处理模块提供两种方式的JTAG调试。一种方式是使用TI的XDS510仿真器和JTAG仿真协议给信号处理模块下载程序,在软件开发和调试时控制程序的执行。另一种方式是使用TI的代码编译开发环境和Pentek的SwiftNet通信协议给信号处理模块下载程序和进行调试。这两种方式可通过一个选择器进行选择使用。

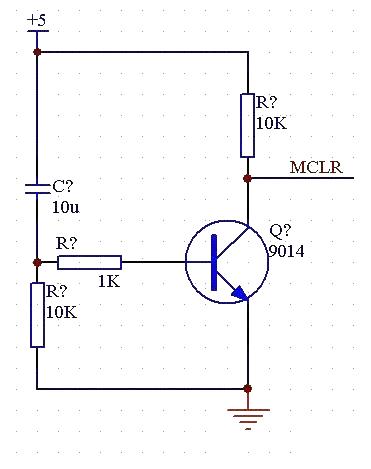

该信号处理板上有4片DSP,需要进行多处理器仿真调试,将DSP的JTAG端口和JTAG仿真器或JTAG控制器间以菊花链方式互连。JTAG调试接口电路如图2所示。

3系统软件设计

随着嵌入式系统应用范围不断扩大,功能也越来越强。对于不同的系统应用需要采用定制信号处理算法。

在实时操作系统支持下开发DSP算法,方便快捷,程序思路清晰,便于代码调试和重用,但是目前大多数DSP实际应用中,仍然采用与早期单片机开发一样的开发方式,用汇编语言直接在硬件层上开发。开发模式的局限,已经严重影响了DSP以及嵌入式系统应用的发展。

并且随着对DSP系统性能要求的迅速提高,DSP软件将会日益复杂,特别是开发大规模并行系统的软件,处理机之间的通信与同步、资源管理、并行任务分配等都是相当繁重的工作。如果完全由程序员手工完成,将增加研发周期,软件质量也难以保证。因此,需要将这些底层的工作交给系统软件来处理,程序员的精力集中于信号处理算法的实现。

信号处理模块主要承担高速实时信号处理任务,使用DSP阵列。如上所述,并行DSP上使用操作系统,将会使复杂的并行程序开发变得相对容易并且效率高。

因此,可以考虑选择系统性能较好并且开发工具齐全的COTS产品,在此基础上进行二次开发,将并行调试技术、负载平衡技术等融合进去。

VSPWorks操作系统是Wind River公司推出的用于DSP的内存占用量小的高性能实时操作系统。VSPWorks RTOS能够与VxWorks RTOS进行通信,这样开发者就可以很容易设计出DSP与通用处理器组合在一起的系统。因此,在实现信号处理模块的操作系统时,选用VSPWorks操作系统为基础,扩充并行调试和负载平衡等功能。另外,还要考虑系统的容错和重构等问题。

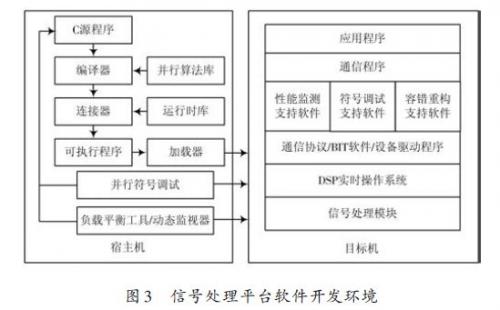

作为通用的信号处理平台,是否受用户欢迎,很大程度并不在于技术的先进性,而在于其开发工具是否友好,开发环境是否完备。该信号处理模块为了方便用户应用,提供良好的集成开发环境(IDE),在IDE中不但包括编辑、编译、连接等一般工具,另外还针对并行系统开发的要求提供了任务加载工具、并行调试工具和负载平衡分析工具等。该开发环境在宿主机上运行,通过调试口(如RS232、JTAG)与目标系统连接。

该信号处理模块软件开发环境包含三个高度集成的部分:运行在宿主机和目标机上的强有力的交叉开发工具和实用程序;运行在目标机上的高性能、可裁剪的实时操作系统;连接宿主机和目标机的多种通信方式,如:以太网、串口线、仿真器等。信号处理模块软件开发环境如图3所示。

4结语

本文通过对信号处理实时性、通用性需求的深入研究,提出了基于TMS320C6701处理器的高性能通用信号处理平台系统结构,重点论述了该平台的通信网络、存储器系统、调试电路等的设计,实现了支持信号处理器的实时操作系统VSPWorks配置,完善了信号处理平台软件开发环境。通过把不同分辨率的合成孔径雷达成像的计算过程映射到不同规模的信号处理模块组成的并行信号处理系统上,处理能力、存储容量、通信带宽等均能满足系统需求,证明了该信号处理平台的通用性、可扩展性及应对大规模浮点处理的有效性。

评论