利用陷波滤波器的自动调谐电路设计

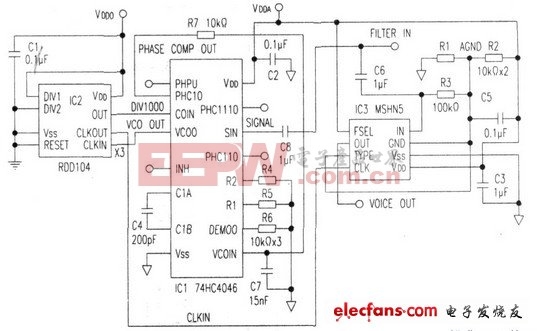

本设计电路如附图所示,使用IC1(74HC4046PLI.锁相环)集成电路芯片,工作频率1MHz.以改善系统的抗噪音度。IC2.一个LSI计算机系统公司生产的RDD104集成电路芯片,在一个8引脚封装中提供1000比1分配器。IC3.混合信号集成的MSHN51000比1时钟角落开关电容器高通,陷波滤波器.采用流行的8脚封装。

将IC1的vco(压控振荡器)的输出(vcoo)馈送进IC2的时钟输入,IC2应用DIV1和DIV2能完成10、100、1000和100100比l的分配,再将RDD104的输出连接到IC1的COIN.通过使用IC1的EX/OR相位比较器,能提高抗噪音度。将fiLTEr输入信号加在IC1(filter)和IC3(filter)的两者输入端.IC2的CLK-OUT脚驱动IC3的时钟。 该MSHN5,IC3,具有可选择高通滤波器和可选择陷波滤波器。当你将FSEL弓1脚接高电位,它选择陷波.将TYPE接AGND选择狭窄陷波滤波器。此步骤保证从带有信息损耗的输入信号中消除仅有的一个音调。IC3的1000比l时钟角落比率减少失真信号会影响输出的机会。对于话音应用,例如500kHz或更高的无信号将可能更名进入通带。一个样品装置在789.13kHz的时钟频率,1000倍于输入信号使用789.13MHz的输入频率。该锁相环跟踪输入,将陷波滤波器移动到1.24kHz。

评论