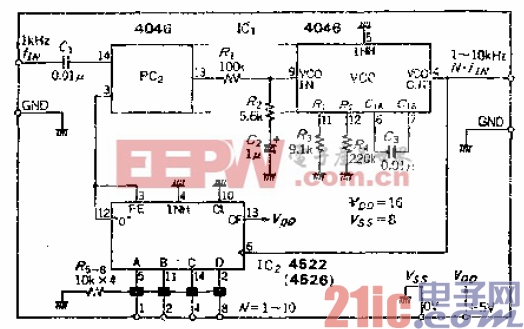

采用PLL(锁相环)IC的频率N(1至10)倍增电路

具有PLL主要功能的C- MOSIC4046是一种最高工作

频率为iMHz的集成电路,将其与可编程除法器连接,便可

构成把输入频率递增Ⅳ倍的电路。相位比较器PC2是检查,,Ⅳ

与Ⅳ分频器输出的频率1相位是否相等的电路,它输出

)~vP-P的信号,经环路滤波器(吼-R2,G皂)滤波后对

vco的振荡频率进行控制。vco的可变范围jf田-f一,∞In就是

从输入频率fiv到N- ffw。考虑刊电路的误差和长期稳定性,

实际上增加了若干安全余量。

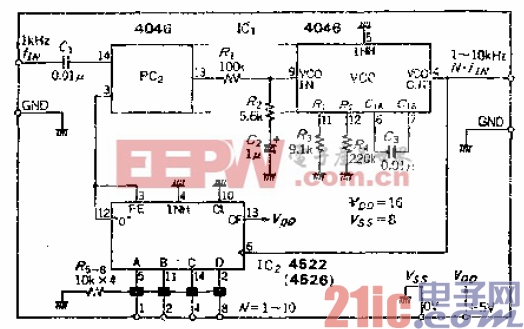

具有PLL主要功能的C- MOSIC4046是一种最高工作

频率为iMHz的集成电路,将其与可编程除法器连接,便可

构成把输入频率递增Ⅳ倍的电路。相位比较器PC2是检查,,Ⅳ

与Ⅳ分频器输出的频率1相位是否相等的电路,它输出

)~vP-P的信号,经环路滤波器(吼-R2,G皂)滤波后对

vco的振荡频率进行控制。vco的可变范围jf田-f一,∞In就是

从输入频率fiv到N- ffw。考虑刊电路的误差和长期稳定性,

实际上增加了若干安全余量。

评论