除法运算电路图及原理

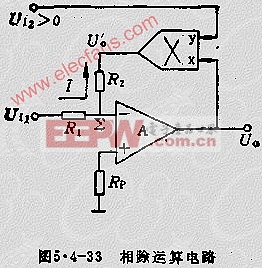

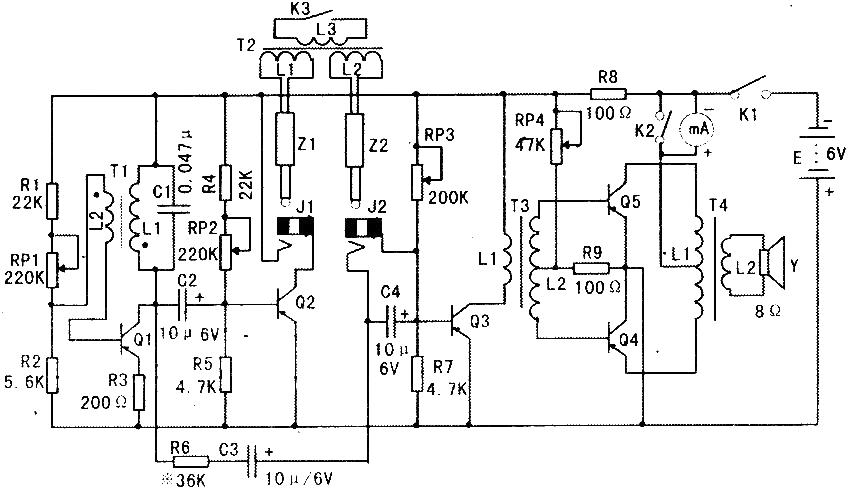

图5.4-33为除法运算电路。将乘法器置于运算放大器的负反馈环路中,则可构成除法运算电路。由图知,∑点为滤地点,R1=R2,则必有:

必须指出,在图5.4-33电路中,为了得到适当的反馈极性,输入信号UI2,必须是正的,否则正反馈将导致运算放大器停止正常工作而闭锁于电源电压。因此,图5.4-33所示的除法电路是一个Ⅱ象限除法器。

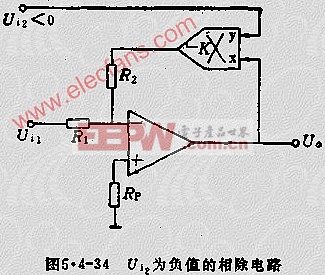

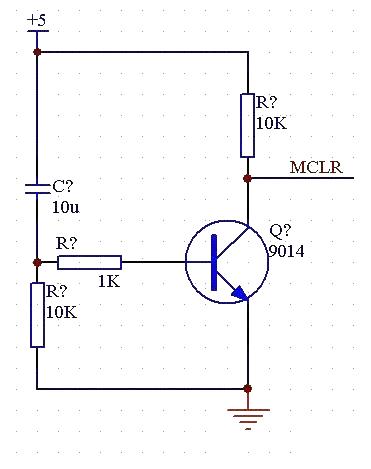

如果UI2为负值,则应采用图5.4-34所示电路。该电路是在反馈回路中引入负相乘增益乘法器。为了得到适当的反馈极性,输入信号UI2必须是负的。

评论