正交I/Q解调器ADL5382与16位连续时间Σ-Δ型ADC AD9262接口,实现射频到比特流解决方案 (CN0062)

这种双芯片解决方案由 ADL5382和AD9262 组成,可提供具有优化性能、低成本和最小电路板空间的射频到比特流解决方案。该双芯片组合只用一个频率转换步骤,可直接将RF通道转换为基带,而无需中频转换。频率转换由ADL5382完成,它是一款宽带正交I/Q解调器,涵盖从700 MHz到2.7 GHz的RF输入频率范围。ADL5382之后接AD9262,它是一款16位、双通道、连续时间Σ-Δ型ADC。连续时间Σ-Δ型架构的特性允许解调器与ADC直接相连,因此,ADC驱动和抗混叠要求得以降低。本电路易于使用,只需极少的支持电路和电路板空间。

双芯片解决方案非常适合下列应用:支持CDMA2000、W-CDMA、WiMAX和LTE的正交接收机;正交采样仪表;医疗设备;以及雷达。特别是在正交接收机系统中,ADL5382可提供RF带宽,同时AD9262便于集成,并提供集成的直流与正交误差校正算法。在直接变频或其它正交系统中,实部(I)与虚部(Q)信号路径之间的不匹配会导致正(负)频谱中的频率在负(正)频谱中形成镜像。这些不匹配可能源于ADL5382或ADC信号链本身任何器件的增益或相位不匹配。AD9262的集成正交误差校正(QEC)算法会尝试测量并校正I与Q信号路径的振幅和相位不平衡,以实现单靠模拟途径无法实现的更高水平镜像抑制。直流校正是AD9262 QEC功能的一部分,它在DC条件下应用一个陷波滤波器,以消除基带信号中的LO转RF泄漏和直流失调。

|

|

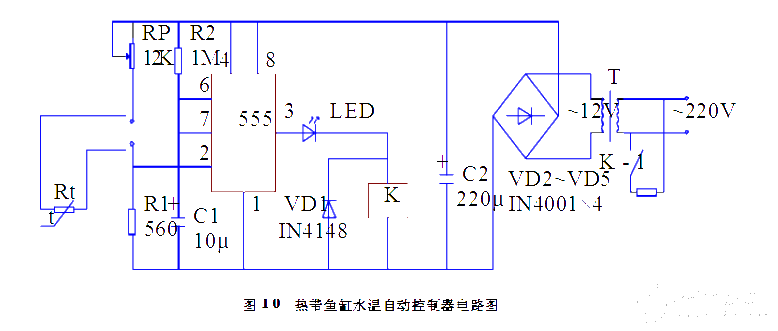

图1. 直接射频到比特流应用中ADL5382与AD9262之间的接口(原理示意图,所有连接和去耦均未显示)

|

图1显示了这种双芯片解决方案,它只需极少的支持电路,便可执行从射频到比特流的直接下变频转换。ADL5382支持700 MHz至2.7 GHz的LO和RF频率范围。LO和RF端口应通过巴伦以差分方式驱动,推荐的巴伦为Mini Circuits TC1-1-13+。LO和RF输入针对50 Ω宽带匹配而设计,应采用1000 pF电容实现交流耦合。另外,必须将以地为参考的扼流圈电感与RFIP和RFIN相连(推荐值为33 nH ,Coilcraft 0603CS-33NX),以提供适当的偏置。扼流圈电感用于提供极低电阻的对地直流路径,以及在RF频率时提供高交流阻抗,从而不影响RF输入阻抗。

ADL5382的I/Q输出可以直接与AD9262的ADC输入相连。这种无缝接口可通过连续时间Σ-Δ输入结构来实现。与传统的开关电容设计不同,AD9262为阻性输入。VIN+与VIN−引脚之间的差分输入阻抗为固定的1000 Ω电阻。这一高输入阻抗可进一步优化ADL5382的线性输入接口。此外,连续时间Σ-Δ架构本身拥有抗混叠功能。因此,ADL5382与AD9262之间可以不需要滤波器网络。根据应用和系统设计要求,对于较大的带外阻塞器,可能需要使用低阶修平滤波器。

外部时钟输入或集成的整数N分频PLL提供过采样连续时间Σ-Δ调制器所需的640 MHz内部时钟。片内抽取滤波器和采样速率转换器可将调制器数据速率从640 MSPS降至用户定义的数据速率(30 MSPS至160 MSPS),从而实现更高效、更直接的接口。

ADL5382与AD9262接口时的一个重要考量,就是要实现AD9262的通道A和通道B输入所要求的适当共模电平。AD9262的VINxA/VINxB输入引脚要求1.8 V的共模电压,而ADL5382的I/Q输出的共模电压为VPOS − 2.8 V。VPOS为ADL5382的正电源电压,其标称值为+5 V。ADL5382与AD9262之间要达到同等的共模电平,需将一个串联电阻RCM放在VPOS与ADL5382的引脚18之间。引脚18规定了I/Q输出的共模电压,因此,在VPOS = 5 V时,要实现1.8 V共模电压,它的理想值为4.6 V。该串联电阻应设置为较低的4.3 Ω。由于流入引脚18的电流为91 mA,因此该电阻将产生0.39 V的压降,而电源电压为5 V,因此引脚18的电压大约为4.6 V,这样输出共模电压值为所需的1.8 V。

这种采用ADL5382和AD9262的射频到比特流整体解决方案可大幅节省印刷电路板空间,易于使用,同时动态性能达到最佳。由于不需要较高阶抗混叠滤波器和驱动器放大器,因此整体设计更为紧凑。此外,ADL5382和AD9262的封装尺寸均很小,可进一步节省印刷电路板空间。ADL5382提供24引脚、4 mm x 4 mm LFCSP封装,AD9262提供9 mm x 9 mm LFCSP封装。由ADL5382和AD9262构成的完整解决方案在900 MHz时的输入IP3为33 dBm,输入IP2优于70 dBm。可用系统带宽为10 MHz(实信号)或20 MHz(复信号)。AD9262的数字输出能够提供30 MHz至160 MHz可编程输出数据速率。

本电路必须构建在具有较大面积接地层的多层电路板上。为实现最佳性能,必须采用适当的布局、接地和去耦技术(请参考教程MT-031和MT-101)。

ADL538x系列解调器与AD926x系列连续时间Σ-Δ型ADC可提供众多RF频率范围和数字输出配置选择。根据应用和性能要求,一种配置可能优于另一种配置。解调器的选择包括ADL5380和ADL5382。与ADL5382相比, ADL5380 可提供更宽的RF频率范围(400 MHz至6 GHz)。不过,必须在线性性能与带宽之间取得平衡。ADL5382或ADL5380均可直接与AD9262或 AD9267接口,以构成完整的射频到比特流双芯片解决方案。AD9262包含连续时间Σ-Δ调制器和后端数字信号处理电路,可提供30 MSPS至160 MSPS的CMOS输出数据速率。AD9267仅包含Σ-Δ调制器,提供640 MSPS的固定4位LVDS输出数据速率。希望自行调理信号的客户可以选择AD9267。解调器与ADC的组合可提供四种配置,每种配置均有其优势和弱点。因此,需要通过细致的系统分析来确定最适合应用的配置。

评论