基于FPGA的AVS视频解码芯片仿真和验证平台设计

AVS是我国具备自主知识产权的第二代信源编码标准,其编码效率比MPEG-2高2~3倍,与AVC相当,但技术方案简洁,芯片实现复杂度低,是一套包含系统、视频、音频和媒体版权管理在内的完整标准体系,为数字音视频产业提供了全面的解决方案。

从2012年11月1日起,AVS标准将被强制执行,届时,所有在中国内地上市的地面数字电视接收机(包括机顶盒、一体机)必须内置AVS解码功能,否则将无法销售。由此,在未来十年时间内,高清晰度/标准清晰度AVS解码芯片的国内需求量年均将达到4 000多万片。

在芯片设计中,验证所花费的时间约占整个设计周期的70%~80%。验证成为大规模集成电路设计的主要瓶颈。一方面,视频解码器需要对大量的一致性测试码流进行验证,在考虑时序信息以后,软件的仿真速度非常慢,因此,需要基于FPGA的硬件仿真平台来提高仿真和验证的速度。另一方面,门数百万级以上的芯片设计每次投片费用巨大,投片前进行基于FPGA的验证是保证投片成功的一个必不可少的环节。

当前关于视频解码芯片的FPGA验证平台的文献并不多。参考文献[2]用2块VirtexE系列的FPGA搭建了视频解码芯片的验证平台;参考文献[2]则采用Xilinx公司的两片FPGA和Altera公司的2片EP2C35 FPGA完成验证平台的设计。本文针对视频解码器芯片的仿真和验证要求,通过对验证平台框架的优化,提出基于1块Altera的FPGA芯片,设计实现视频解码器的硬件验证平台。

1 验证平台组成和设计

硬件验证平台应该具有可重用的特点。在芯片的设计阶段,硬件验证平台可以作为仿真验证平台,要求能够独立完成整个视频解码的过程。一方面可以将视频解码系统的硬件模块载入,以验证硬件模块的功能;另一方面可以载入视频解码系统的软件部分,让硬件模块和软件模块在一个平台下真正实现软硬件协同工作,以验证整个解码系统的功能,实现视频解码的全过程。

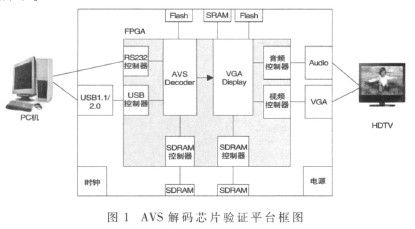

本验证平台以Altera公司的DE2多媒体开发平台为主体,在FPGA内嵌入Nios II软核处理器,结合Nios II可自定义CPU指令和用户外设的特点,配合PC机软件程序、VGA显示器以及自定义SDRM存储器端口控制模块,搭建出一个完整的视频解码芯片验证平台,如图1所示。

考虑到方便设计和占用资源少的原因,该验证平台仅用一块FPGA,故将其分为两部分来设计:视频解码部分和VGA显示部分。其中,视频解码部分可以独立完成视频码流解码过程,将输入的视频文件解码成YUV文件;同时,可将设计的AVS视频解码器的硬件模块载入,以验证硬件模块的功能,并且为分析所设计模块的性能参数提供可靠依据。VGA显示部分主要控制VGA显示器显示解码生成的YUV文件。这两部分构成了一个“视频解码—VGA显示”的完整的验证平台。

1.1 视频解码设计

该系统主要分为视频解码系统硬件设计和软件程序开发。

1.1.1 视频解码硬件设计

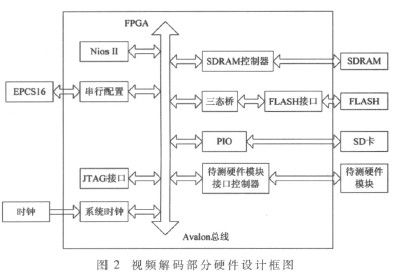

视频解码系统硬件设计框图如图2所示,采用一块Altera EP2C35F672C6 FPGA,它能提供丰富的内存资源和容量,以及新算法资源,增强时钟管理支持,其结构体系将使系统性能达到更高层次,扩大输入输出带宽,提高时钟频率、内存速度和数据处理速度。在FPGA上实现Nios II软核CPU、SDRAM、Flash、Timer、Epcs controller等模块相连。Nios II 软核CPU和其他IP模块之间通过Avalon片上总线相连,该总线规定了主部件和从部件之间进行连接的端口和通信的时序。该部分允许将设计的硬件模块或者AVS视频解码系统挂接到Avalon总线上,通过Nios II软核处理器的控制,与PC机中的软件解码程序协同工作,共同完成视频解码过程。同时还能够计算出其所占用资源以及加入硬件模块后所节省的时间,便于准确分析所验证硬件模块的性能参数。

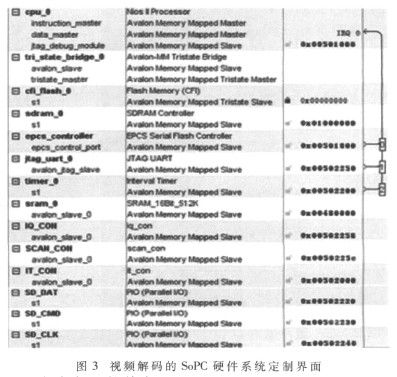

根据系统的功能要求和Nios II软核处理器的高度可配置性,通过硬件开发工具SoPC Builder定制的硬件系统框图如图3所。Nios II系统用CFI-Flash存储输入的视频频码流文件,SDRAM用作运行程序的内存。同时加入了SD卡,预留存储以后需要解码的大容量视频文件,生成的解码文件暂存在PC机上,这样极大地减少了片上RAM的使用率。

1.1.2 视频解码软件实现

在完成系统的硬件设计后, 利用Altera提供的Nios II IDE软件,实现应用程序的软件设计,主要是CPU控制主程序以及能够独立完成视频解码的软件程序。将待验证的硬件模块挂接到Avalon总线上,此时FPGA中既放入解码系统的硬件模块,也放入了解码系统的软件模块,RISC CPU 完成PC机上CPU的功能,控制系统软硬件模块的运行。待解码的AVS视频码流通过USB接口送给验证平台上的视频解码系统,RISC CPU协调放在FPGA中的AVS解码系统硬件模块和软件模块以完成解码。AVS数据经过解码,转换成可以播放的YUV格式的视频数据。

1.2 VGA显示设计

该部分将上述视频解码软件转换成的YUV数据经过视频控制器做一些后处理和视频格式转换的工作,然后将YUV视频数据通过VGA控制接口,最后在VGA显示器上将这些视频信号显示出来。下面分别介绍该部分的硬件开发设计和软件程序实现。

1.2.1 VGA显示硬件设计

在该设计中,Nios II软核处理器主要完成CFI-Flash和SDRAM存储器的读写操作,并且控制VGA的显示。在SoPC Builder中搭建VGA显示部分的硬件系统。针对系统的要求,在FPGA外围连接了SRAM、SDRAM和Flash等存储器,它们可以满足视频处理过程中对于存储器的不同要求。其中,SRAM作为CPU控制主程序运行的内存;Flash用于存储播放的YUV视频文件;SDRAM容量大、速度快,用于VGA显示的缓存,确保视频播放的流畅。并没有直接将SDRAM挂接到Avalon总线上,而是自己编写了SDRAM端口控制器,再将其挂接到Avalon总线上,通过端口控制器对SDRAM进行读写操作。

视频文件从Flash写到SDRAM后,再经过VGA控制器显示到显示器上。VGA控制器采用Verilog语言编写,使其具有更高执行性能,如图4所示。

1.2.2 VGA显示软件设计

在Nios II软件开发过程中,使用Altera提供的IO操作函数对SDRAM进行写操作,并且利用Altera提供的API函数对Flash进行读操作。具体函数如下:

Alt_flash_fd * fd

fd = alt_flash_open_dev("/dev/cfi_flash");

alt_read_flash(fd, CFI_FLASH_BASE+202752*j, buf, 202752);

for(i=0; i<101376;i++)

{ IOWR_16DIRECT (SDRAM_0_BASE, 0, buf[i]);

2 验证实例

基于提出的AVS视频解码芯片验证框架,实现了基于FPGA的AVS解码芯片验证平台,验证平台分为视频解码系统和VGA显示系统两部分。视频解码系统可以嵌入待验证的硬件模块或下载待验证的视频解码器。基于该解码芯片验证平台,完成了AVS解码芯片以及其中帧内预测、熵解码和环路滤波等主要硬件模块的验证。相对于Modelsim的软件仿真,硬件验证平台大大提高了验证速度,同时也为成功投片提供了可靠保障。图5为验证平台中视频解码系统的软硬件解码过程。

在硬件系统设计过程中,FPGA验证已成为了系统设计的重要一环。本文提出了视频解码芯片的验证框架,并设计实现了基于FPGA的视频解码芯片验证平台。该硬件验证平台包括视频解码系统和VGA显示系统两部分,通过视频解码系统可以嵌入待验证的视频解码系统和硬件模块,提高了验证速度和效率。该验证平台具有操作灵活、验证效率高、可重用性强和易扩展为验证其他视频标准解码芯片的验证平台等优点。基于该验证平台已实现了多个硬件模块和AVS视频解码芯片的验证。

评论