连续脉冲信号延迟线的实现

摘 要:用VHDL语言设计一个连续脉冲信号延迟线,通过对连续脉冲信号的可控延迟来仿真脉冲多普勒雷达对动目标的跟踪回波包络,分析并建立了直接采样法的系统模型。

关键词:VHDL,CPLD,雷达回波,延迟线

1 引言

在延迟控制系统及目标跟踪仿真测试系统等应用系统中,要使用脉冲延迟器来实现脉冲信号延迟控制功能。传统的延迟继电器无法满足大动态范围、高精度以及高速实时控制等诸多系统要求。现有的专用脉冲延迟器件(如AD9500/9501等)虽然在精度、速度方面可以保证,但对于比较大的动态范围实现比较困难,而且在连续脉冲信号的延迟时间逐渐减小时,无法实现负增量延迟。针对以上问题,我们采用VHDL对CPLD进行编程,通过直接采样法实现大范围动态连续脉冲信号可控延迟功能。

2 系统功能

本系统拟定对频率范围在200~600kHz的TTL电平脉冲序列进行延迟处理,延迟范围600ns~170μs,分辨率为100ns。延迟精度50ns,延迟量刷新周期大于脉冲信号周期但要小于1ms。

3 方案选择

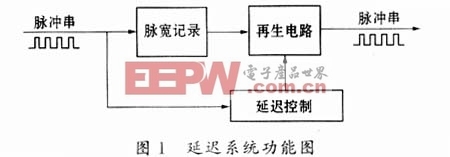

当要处理的信号是单个脉冲信号或连续脉冲的脉冲间隔时间大于脉冲延迟时间时,延迟器只要一级缓冲,不必考虑脉冲串的多脉冲存储和再生问题。这种情况下,可以根据不同精度的要求采用机械延迟(如:延时继电器)、模拟延迟(如:积分延迟)和数字延迟(如:计数器)等手段。如果要无失真恢复脉冲信号,则必须有精确的脉宽测量和恢复电路。见图1。

但当脉冲串的脉冲间隔小于延迟时间时,就有很大的不同。此时必须考虑多脉冲存储和再生的问题,电路必须设定相应的存储器保存多脉冲信息用于再生。可以直接对脉冲串进行采样,然后量化为数字信号进行存储,再利用延迟量来控制信号再生。另外,脉冲信号不同于通常的数字信号,数字信号的占空比一般为固定的50%,所以,无论存储和再生都比较容易,而脉冲信号的占空比是不规则的,随时因场合的变化而变化,所以,要无失真地再生脉冲串信号必须精确记录每一脉冲的脉冲宽度和周期信息。

输入连续脉冲是逻辑电平信号,所以,可以将连续脉冲串信号看作逻辑信号直接使用FIFO进行采样,采样结果只有1和0两种值,所以采样结果只需要一位宽度的FIFO进行存储。为保证电路的精度,采样速度可能比较高,采样速度越高,所需要的FIFO规模越大,对于本设计所要求的精度,即最大延迟170μs,延迟精度50ns,则采样周期必须小于25ns。选择40MHz的采样频率,采样周期为25ns,采样精度±25ns。此时要求FIFO的深度为170000/25=6800bit,为解决在延迟参数切换时造成的系统不连续性,尤其在延迟参数递减时造成的系统信息无法恢复的问题,我们对奇数帧和偶数帧的信号分别进行延迟处理(设每一次延迟参数下的脉冲信号为一帧)。使用控制信号来分时选通两种FIFO进行清除和采样以及信号输出。

4 方案实现

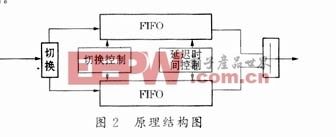

具体方案原理见图2,FIFO的数量为2个。用2个FIFO轮流存储脉冲的采样值,延迟时间相同的脉冲存储在同一个FIFO中,延迟时间不同的脉冲存在不同的FIFO中,延迟时间每刷新一次,存储FIFO切换一次。输出信号由两个FIFO的输出相或而得。

从图2可以看出:该设计主要有切换控制、延迟时间控制、FIFO等组成部分。信号由输入端进入器件,经切换开关,由切换控制选择存储FIFO,直接采样存储到不同的FIFO中去,由延迟控制器控制延迟时间,最后两个FIFO的输出相或得到输出脉冲。

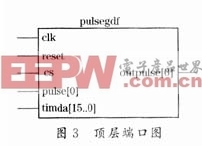

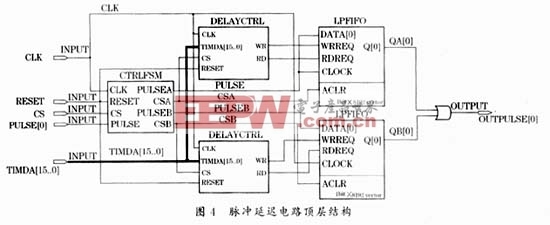

用可编程器件进行设计时,应采用自顶向下的设计方法,脉冲延迟电路的端口图如图3所示。首先,把系统划为几个模块,再对各个模块进行设计,完成电路设计。在设计脉冲延迟电路时,对电路模块进行了划分,分成了切换控制、延迟控制、存储FIFO等模块,由各模块之间的控制关系构成了系统的结构框图如图4所示。

端口说明:

?clk为系统时钟,应用于整个电路,输入端口;

?reset为系统复位信号,高电平有效,输入

?cs为延迟时间更新控制信号,控制延迟时间的改变,低电平有效,输入端口;

?pulse为调制脉冲,被处理脉冲,输入端口;

?timda[15..0]为延迟时间数据,延迟时间的大小由此信号得到,为16位数据线,输入端口;

?outpulse为调制脉冲输出信号,输出延迟后的脉冲,输出端口。

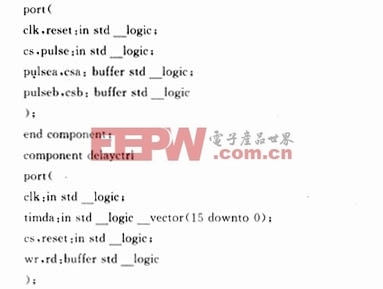

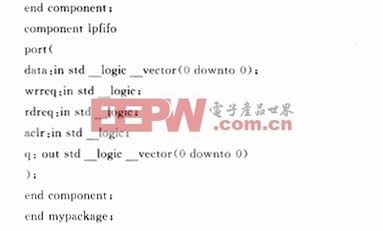

该方案设计的脉冲延迟电路由三类元件组成,分别是切换控制元件(CTRLFSM)、延迟控制元件(DELAYCTRL)、存储单元(LPFIFO)。下面对各元件进行设计:

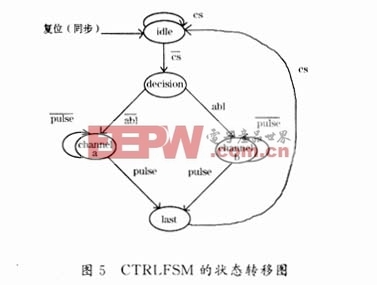

CTRLFSM 该元件为时序逻辑电路,可设计成有限状态机。状态转移图如图5所示:首先,一个同步复位信号使该状态机进入空闲态(idle)。当cs信号有效后,在下一个时钟周期进入decision状态,再根据ab1信号分别进入channela或channelb状态,判断并发选择信号。当pulse有效时进入last状态,进行切换,切换后,等待cs无效,以便返回空闲状态。

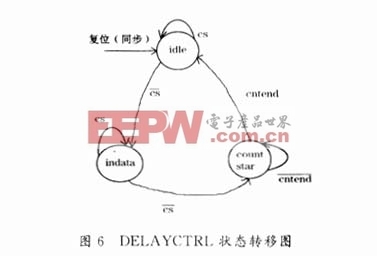

DELAYCTRL 延迟时间控制元件完成延迟时间的刷新和延迟时间的定时控制,由一个有限状态,计数器完成定时。定时计数器为简单的16位计数器,设计比较简单,在此不再赘述。这里只介绍一下延迟控制器的设计,其状态转移图如图6所示。延时控制器包括三个状态:空闲状态(idle)、延迟时间刷新状态(indata)、延时状态(countstar)。

LPFIFO 存储单元可以自己设计,也可以调用已有参数化lpm模块。为简化设计,提高器件的利用率,本方案中直接调用lpm模块,具体调用过程可由软件生成。

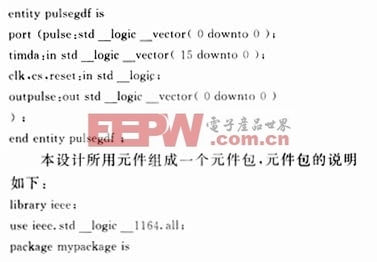

综上所述,可以写出脉冲延迟电路的实体说明如下(VHDL语言):

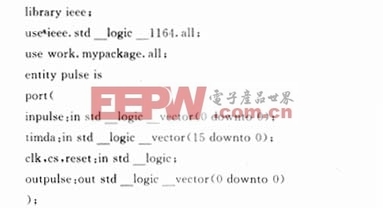

说明了上述元件包以后,可以根据顶层结构图将各元件连接起来,得到脉冲延迟电路的顶层描述VHDL语言代码如下:

本设计选择Altera的FLEX 10KE产品,Altera FLEX 10KE的产品集成度更高,工作频率高、系统传输延迟更小。采样周期为25ns,采样精度±25ns。要求FIFO的深度为2×170000/25=2×6800bit,Altera FLEX 10KE的EAB规模为2048×2bit,对于40MHz的采样时钟,每一个FIFO至少需要4块EAB(6800/20483),共8块,此时选用EPF10K50E比较合适,电路板设计采用Mentor Graphic EDA产品,CPLD设计采用Altera的MaxplusII。为了延迟系统能尽量独立工作,采用主动配置方式设计系统,选用Altera的EPC2电可擦除EPROM来配置系统。电路PCB及电路实物图略。

5 系统仿真

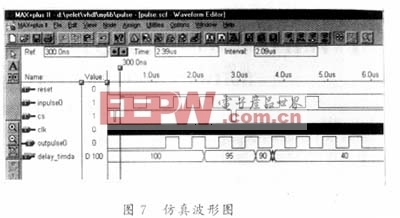

完成设计后,用MAX+PLUS II软件进行后仿真,仿真结果如图7所示。

从图7可以看出,输入信号与输出信号延迟可变,输出的脉冲信数与输入的脉冲个数相等。符合设计要求,满应用需要。

6 结束语

本设计不同于现有的延迟电路,它可以对实时连续信号进行大范围动态延迟,不但可以实现正增量延迟,更重要的是可以实现负增量动态延迟,这为雷达回波模拟提供了可能,同时延迟范围不局限于通常延迟电路小于一个脉冲周期的延迟时间,在不丢失脉冲的前提下,实现了多周期大范围动态延迟。该方法不但可以完成TTL电平信号的大范围动态延迟,而且只要适当增加位深度,就可以将该方法用于对模拟信号进行采样延迟,为各种信号大范围实时动态延迟提供了很好的思路。

参考文献

1 侯伯亨,顾新编著.VHDL硬件描述语言与数字逻辑电路设计.西安:西安电子科技大学出版社,1999,1

2 曾繁泰,陈美金著.VHDL程序设计.北京:清华大学出版社,2001,2

3 林敏,方颖立编著.VHDL数字系统设计与高层次综合.北京:电子工业出版社,2002,1

评论