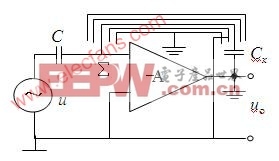

利用运算放大器式电路虚地点减小电缆电容原理

利用运算放大器的虚地来减小引线电缆寄生电容CP的原理图

采用运算放大器法

下图是利用运算放大器的虚地来减小引线电缆寄生电容CP的原理图。图中电容传感器的一个电极经电缆芯线接运算放大器的虚地Σ点,电缆的屏蔽层接仪器地,这时与传感器电容相并联的为等效电缆电容Cp/(1+A),因而大大地减小了电缆电容的影响。外界干扰因屏蔽层接仪器地,对芯线不起作用。

传感器的另一电极接大地,用来防止外电场的干扰。若采用双屏蔽层电缆,其外屏蔽层接大地,干扰影响就更小。实际上,这是一种不完全的电缆“驱动技术”,结构较简单。开环放大倍数A越大,精度越高。选择足够大的A值可保证所需的测量精度。

图5.3-12 利用运算放大器式电路虚地点减小电缆电容原理图

评论