基于FPGA+DDS的正弦信号发生器的设计

1971年,美国学者TIERNCY J、TADER C M和GOLD B在《A Digital Frequeney Synthesizer》一文中提出了以全数字技术,从相位概念出发直接合成所需波形的一种新的频率合成原理,称之为直接数字频率合成器DDS(Direct Digitial Frequency Synthesis)[1].这是频率合成技术的一次重大革命,但限于当时微电子技术和数字信号处理技术的限制,DDS并没有得到足够的重视。随着现代超大规模集成电路集成工艺的高速发展,数字频率合成技术得到了质的飞跃,它在相对带宽、频率转换时间、相位连续性、正交输出、高分辨率以及集成化等一系列性能指标方面,已远远超过了传统频率合成技术所能达到的水平。因此广泛用于通信、宇航、遥控遥测、仪器仪表等各项电子领域[1-2].

目前实现DDS的技术方案大致分为两种,一是用专用的DDS芯片来实现。常用的DDS芯片有ADI公司的AD9xxx系列,如其中的AD9913,它具有高达100 MHz的模拟输出,内部集成一个10位的D/A转换器,频率分辨率≥0.058 Hz,相调谐分辨率为0.022°[3].另一种是用FPGA来实现。可编程的FPGA器件具有内部资源丰富、处理速度快、可在系统内编程并有强大的EDA设计软件支持等特点。因此,基于FPGA的设计相对于专用DDS芯片,可使电路设计更加灵活、提高系统的可靠性、缩短设计周期、降低成本。所以,采用FPGA设计的DDS系统具有很高的性价比。

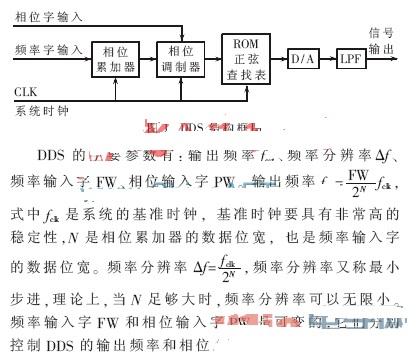

1 DDS基本原理

直接数字频率合成的理论依据是采样定理,即先对一个完整周期的正弦波进行N点采样,然后把采样点存储在ROM中构成一个查找表,频率合成时,相位累加器在参考时钟的作用下控制ROM中数据的输出。ROM的输出经过D/A转换,将一个阶梯化的信号(即采样信号)通过一个理想的低通滤波器,就得到符合要求的模拟信号。

DDS的基本结构如图1所示,主要由相位累加器、相位调制器、波形ROM查找表、DAC和低通滤波器(LPF)构成。其中相位累加器、相位调制器、波形ROM查找表是DDS结构中的数字部分,由于具有数控频率合成的功能,又合称为NCO(Numerically Controlled Oscillators)。

2 DDS波形发生器的系统设计

本系统分为软件设计和硬件设计两部分,软件部分主要是基于FPGA的程序设计,硬件部分包括D/A转换和低通滤波器设计。

2.1 VHDL程序设计

2.1.1定制波形数据文件

在设计DDS信号源之前,先建立一个储存波形数据的ROM,储存波形数据文件有。mif和。hex两种格式。。mif和。hex格式的文件可以用Quartuas II建立,也可以用Quartuas II以外的编辑器设计,如MATLAB、C语言等。本系统的ROM文件一个周期有1 024个点的正弦波数据、10 bit地址线和10 bit数据线。

图2 DDS的软件设计框图

2.2相关电路设计

2.2.1 D/A转换电路

位于波形输出ROM后的D/A单元,是将数字量形式的波形幅值转换成所要求的合成频率的模拟量形式信号[4].由于储存波形的ROM具有10 bit的输出,所以采用10 bit的DAC将FPGA输出的数字信号转换成模拟信号。本系统采用ADI公司的10 bit COMS数模转换芯片AD5432,AD5432的驱动电压为3 V~5.5 V,具有50 MHz的串行接口、10 MHz的乘法带宽、2.5 MS/s的更新速率,采用±10 V的参考输入,输出为电流[5].

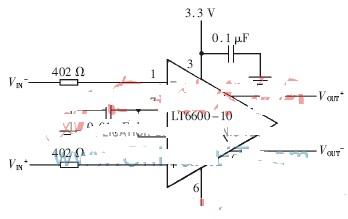

2.2.2滤波电路

经由DAC的输出信号实际上是阶梯模拟信号,需利用低通滤波器滤除波形的杂波,并进行平滑处理。由于本系统的最高输出频率为10 MHz,所以选取的低通滤波器的截止频率也应为10 MHz.为了减少系统体积,节省设计时间,提高系统的可靠性,本系统选用凌特公司LT6600-10低通滤波器。LT6600-10内集成了一个全差分放大器和一个近似于切比雪夫响应的四阶10 MHz低通滤波器,差分增益由两个外部电阻设置[6],其基本连接方式如图3所示。

图3 LT6600-10 的基本连接方式

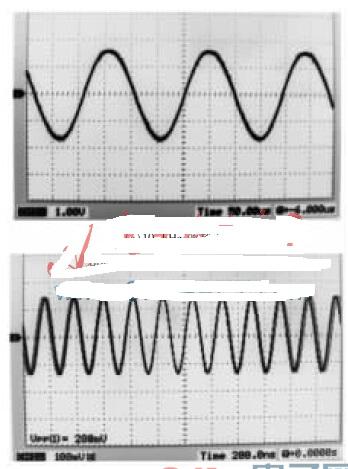

3实验仿真与分析

实验中所用的FPGA芯片为Altera公司的Cyclone III系列,Cyclone III是Altera公司的首款65 nm低成本FPGA,含有5 K~120 K逻辑单元(LE),288个数字信号处理(DSP)乘法器,存储器达到4 Mbit.Cyclone III系列比前一代产品每逻辑单元成本降低20%,使设计人员能够更多地在成本敏感的应用中使用FPGA.系统所用的测试频率(参考频率)为50 MHz,调试好系统,使系统的输出从1 kHz~10 MHz递增,并改变输出波形的相位,输出波形的相位变化范围为0°~360°。经示波器测试,系统的输出波形形状良好,输出波形的实测频率与理论计算值的绝对误差小于0.1%,满足设计要求,有较好的实用价值。图4为实验的输出波形。

图4 实验输出波形

产生测试信号的仪器统称为信号源,也称为信号发生器,它用于产生被测电路所需特定参数的电测试信号。信号发生器用途非常广泛,科学实验、产品研发、生产维修、IC芯片测试中都能见到它的身影,目前市场上大部分信号发生器多采用DDS频率直接合成技术。尽管基于FPGA的DDS信号发生器应用广泛,较传统的信号源有许多优点,但是由于DDS数字化实现的固有特点,决定了其输出频谱杂散较大,又由于DDS内部DAC和ROM的工作速度的限制,使得DDS信号源的最高输出频率受限[7].不过,随着DDS技术的不断完善和发展,其频谱杂散、最高输出频率的性能指标将得到优化,未来将有越来越多的信号发生器采用DDS技术,所以说对DDS进行研究具有很好的现实意义。

评论