新型MP3解码芯片VS1001K及其应用

摘要:VS1001K是芬兰VLSI Solution公司生产的新型MP3解码芯片。该芯片内含高质量的立体声数模转换器(DAC)和耳机驱动电路,支持PCM数据输入。它还具有体积小、功耗低、接口简单、价格便宜等优点。文中介绍了VS1001K的引脚排列、内部结构和主要特点。同时重点介绍了VS1001K的SCI控制接口中各寄存器的功能和地址以及SDI数据接口的操作方法。最后给出了VS1001K的应用电路。

关键词:MP3 编码 播放器 VS1001K

1 引言

目前,INTERNET网上和便携式播放器所使用的MP3音频数据压缩方法已经成为一种公认的行业标准了。这种方法以其压缩率高、音质好而迅速风靡全世界。但实际上,许多MP3播放器的核心就是一片MP3音频解码芯片。VS1001K是芬兰VLSI Solution公司推出的新型MP3解码芯片。该芯片内含高质量的立体声数模转换器(DAC)和耳机驱动电路,它支持PCM数据输入,同时具有体积小、功耗低、接口简单、价格便宜等优点。因而有望成为新型MP3解码器的首选芯片。

2 VS1001K的功能结构

2.1 VS1001K的引脚功能

VS1001K具有两种封装形式:分别为28脚SOIC双列式和49脚BGA球栅阵列式。图1给出了28脚SOIC封装的引脚排列图。各引脚的具体功能说明如表1所列。

表1 VS1001K的引脚功能

| 引脚号 | 引脚名称 | 功 能 |

| 1 | DREQ | 数据请求端口 |

| 2 | DCLK | SDI时钟信号输入端 |

| 3 | SDATA | SDI数据输入端 |

| 4 | BSYNC | 字节同步信号端 |

| 5,9,28 | DVDD | 数字电源 |

| 6,10,27 | DGND | 数字地 |

| 7 | XTALO | 时钟信号输出 |

| 8 | XTALI | 时钟信号输入 |

| 11 | XCS | 片选,低电平有效 |

| 12 | SCLK | SCI时钟输入端 |

| 13 | SI | SCI数据输入端 |

| 14 | SO | SCI数据输出端 |

| 15~17 | TEST0 | 备用测试端口 |

| 18,21,25 | AGND | 模拟地 |

| 19,23 | AVDD | 模拟电源 |

| 20 | RIGHT | 右声道音频输出 |

| 22 | RCAP | 外接电容接入端 |

| 24 | LEFT | 左声道音频输出 |

| 26 | XRESET | 电路复位端,低电平有效 |

表2 SCI寄存器功能

| 寄存器名 | 地 址 | 类 型 |

功 能 |

| MODE | 0x00 | RW | 用于控制VS1001K的操作 |

| STATUS | 0x01 | RW | 当前VS1001K的状态信息 |

| INT_FCTLH | 0x02 | - | 内部寄存器,一般不用 |

| CLOCKF | 0x03 | RW | 控制时钟频率和倍频器 |

| DECODE_TIME | 0x04 | R | 确定解码时间(单位为秒) |

| AUDATA | 0x05 | R | 声音数据 |

| WRAM | 0x06 | W | 用于向程序RAM写入用户程序 |

| WRAMADDR | 0x07 | W | 为WRAM操作设置基地址 |

| HDAT0 | 0x08 | R | 读取MP3表头数据 |

| HDAT1 | 0x09 | R | 读取MP3表头数据 |

| A1ADDR | 0x0A | RW | 确定用户应用程序的开始地址 |

| VOL | 0x0B | RW | 用于音量控制,高、低字节分别为左、右声道。音量取值范围为0~FF,0位最大,FF为最小 |

| RESERVED | 0x0C | - | 保留 |

| A1CTRL[0] | 0x0D | RW | 用于控制用户应用程序 |

| A1CTRL[1] | 0x0E | RW | 用于控制用户应用程序 |

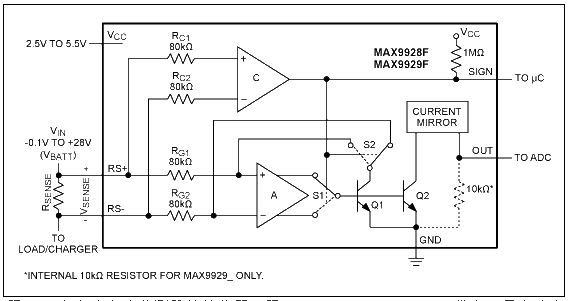

2.2 VS1001K的内部结构

VS1001K解码芯片内部集成有VS DSP处理器,同时它还集成有立体声音频DAC、立体声耳机放大驱动器、以及程序ROM和程序RAM等,此外,VS1001K还带有串行的数据接口和控制接口。图2是VS1001K的内部结构原理框图。

3 VS1001K的工作原理

VS1001K主要通过两个串行接口SCI和SDI来接收外部微处理器传送来控制命令和MP3数据。其中SCI用于接收外部微处理器传送来控制命令,SDI用来接收外部微处理器传送的MP3数据。

3.1 SCI控制接口

对VS1001K的控制主要是通过对SCI中的15个16位寄存器进行操作来实现的。表2所列是SCI的15个16位寄存器的名称、地址、类型和功能说明。实际上,对VS1001K的主要操作都是通过MODE寄存器来完成的,表3给出了MODE寄存器各位的操作功能说明。

表3 MODE寄存器的操作方法

| 位 | 名 称 |

功 能 |

操作说明 |

| 0 | SM_DIFF | 差分输出控制 | 0为正常,1为左声道反相 |

| 1 | SM_FFWD | 快进 | 0为正常快速度,1为快进 |

| 2 | SM_RESET | 软件复位 | 0时不复位,1时复位 |

| 3 | SM_MP12 | 是否解码MP1和2 | 0为只解MP3,1时解码MP1/2/3 |

| 4 | SM_PDOWN | 掉电控制 | 0为上电,1为掉电 |

| 5 | SM_DAC | 数模转换模式控制 | 0为一般MPEG解码,1为PCM解码 |

| 6 | SM_DACMONO | 立体声数模转换控制 | 0为立体声,1为单声道 |

| 7 | SM_BASS | 高/低音增强器 | 0为关,1为开 |

| 8 | SM_DACT | DCLK触发沿 | 0为从MSB开始,1为从LSB开始 |

| 9 | SM_BYTEORD | 字节传送顺序 | 0为上升沿,1为降沿 |

| 10 | SM_IBMODE | 工作模式 | 0为从模式,1为主模式 |

| 11 | SM_IBCLK | VS1001K在主模式工作时,用于DCLK频率设置 | 0时选512kHz,1时选1024kHz |

SCI和外部微处理器的通讯协议包括指令字节、地址字节和16位字三部分。其中指令字节取0X03时为读寄存器,取0X02时为写寄存器;地址字节的主要用途是确定地址寄存器的地址,其范围为0X00~0X0E.而16位字则用于指向指定寄存器写入或读出的值。图3所示是SCI寄存器的读写操作时序。

3.2 SDI数据接口

当外部微处理器通过SDI接口向VS1001K传送MP3数据时,在MODE寄存器的不同设定下,SDI可工作在主、从两种模式。

当SDI在主模式下工作时,其DCLK信号由VS1001K内部产生(具体是512kHz还是1024kHz由MODE寄存器的SM IBCLK位决定),而当SDI工作在从模式时,DCLK由外部输入。

SDI通常以字节为单位来进行数据传送,并在DCLK的上升沿或下降沿(具体由MODE寄存器的SM_DACT位决定)将SDATA数据信号输入。数据传送时采用高位在前还是低位在前是由MODE寄存器的SM DACT位来决定的。SDI采用BSYNC信号来确保数据传送时不出现错位的情况。

图3、图4 点击放大

当SDI在从模式下接收数据时,如果片内FIFO还有足够的空间,VS1001K会发出一个高电平DREQ数据请求信号,以表示可以接收至少32个字节的MP3数据。

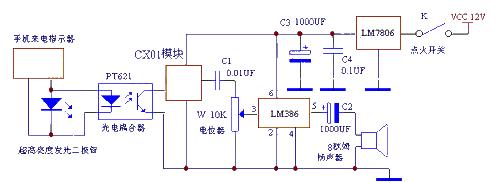

4 VS1001K的应用

图4是VS1001K通过SDI和SCI接口与外部微处理器进行连接的应用电路。从图中可见,由于VS1001K解码器在其芯片内部已经集成了数模转换器和耳机音频驱动电路,因而其外围电路十分简单。实际上,图4电路已经对VS1001K与微处理器的接口电路进行了优化。

关于读写SCI的寄存器或向SDI传送MP3数据的软件编程,对于不同的外部微处理器,其软件编程可能会有所不同。但都不是很复杂。限于篇幅,本文不再赘述。

评论