串行A/D转换器TLC2543与TMS320C25的接口及编程

TMS320C25是TI(TEXAS INSTRUMENT)公司的16位数字信号处理器,它在结构上采用程序存储器和数据存储器分开寻址的哈佛结构,允许取指令和执行指令全部重叠进行。该DSP内含544个字的RAM,4k字的程序存储器ROM,用掩膜方法放置在内部ROM中的程序可以全速运行。TMS320C25内含32位乘法器,可以单指令周期完成16×16位2的补码数相乘,这对诸如卷积等DSP基本算法是有效的。另外,它与专用的DSP指令系统相结合能提高速度和灵活性,每秒执行的指令可达10M条。

TLC2543也是TI公司的产品,它是12位开关电容逐次逼近A/D转换器。每个器件有三个控制输入端:片选(CS)、输入/输出时钟(I/O CLOCK)以及数据输入端(DATA INPUT)。通过一个串行三态输出端与主处理器或其外围的串行口通信,可与主机高速传输数据,可编程输出数据长度和格式。片内含有一个14通道多路器,可从11个模拟输入和三个内部自测电压中选择一个。片内设有采样保持电路。用“转换结束”信号EOC指示转换的完成。系统时钟由片内产生并由I/O CLOCK同步。正、负基准电压(REF+,REF-)由外部提供,通常为VCC或地,两者差值决定输入电压范围。片内转换器使器件有高速(10μs转换时间),高精度(12位分辨率,最大±1LSB的线性误差)和低噪声的特点。TLC2543的引脚排列如图1所示。采用20脚DIP封装。

1. 硬件设计

1.1 TLC2543的简要工作过程

TLC2543的工作过程分为两个周期:I/O周期和实际转换周期。

a. I/O周期

I/O周期由外部提供的I/O CLOCK定义,延续8、12或16个时钟周期,决定于选定的输出数据长度。器件进入I/O周期后同时进行两种操作。

(1)在I/O CLOCK的前8个脉冲的上升沿,以MSB前导方式从DATA INPUT端输入8位数据流到输入寄存器。其中前4位为模拟通道地址,控制14通道模拟多路器从11个模拟输入和三个内部测电压中选通一路送到采样保持电路,该电路从第4个I/O CLOCK脉冲的下降沿开始对所选信号进行采样,直到最后一个I/O CLOCK脉冲的下降沿。I/O周期的时钟脉冲个数与输出数据长度(位数)同时由输入数据的D3、D2位选择为8、12或16。当工作于12或16位时,在前8个时钟脉冲之后,DATA INPUT无效。

(2)在DATA OUT端串行输出8、12或16位数据。当CS保持为低时,第一个数据出现在EOC的上升沿。若转换由CS控制,则第一个输出数据发生在CS的下降沿。这个数据串是前一次转换的结果,在第一个输出数据位之后的每个后续位均由后续的I/O时钟下降沿输出。

b.转换周期

在I/O周期的最后一个I/O CLOCK下降沿之后,EOC变低,采样值保持不变,转换周期开始,片内转换器对采样值进行逐次逼近式A/D转换,其工作由与I/O CLOCK同步的内部时钟控制。转换完成后EOC变高,转换结果锁存在输出数据寄存器中,待下一个I/O周期输出。I/O周期和转换周期交替进行,从而可减小外部的数字噪声对转换精度的影响。

1.2 接口设计

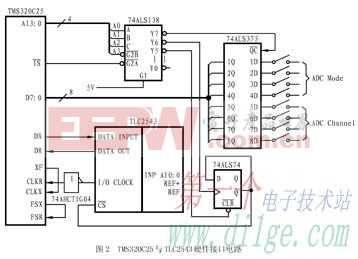

TMS320C25片内有一个全双工串行口,其接收和发送操作都是双向缓冲的。与串行口工作相关的引脚有:DX(发送的串行数据信号),DR(接收的串行数据信号),CLKX(发送时钟信号),CLKR(接收时钟信号),FSX(发送帧同步信号)和FSR(接收帧同步信号)。在DX和DR引脚上的数据分别通过CLKX或CLKR信号记录到TMS320C25的XSR(发送移位寄存器)和RSR(接收移位寄存器)中,XSR和RSR又分别与DXR(数据发送寄存器)和DRR(数据接收寄存器)相连,DXR和DRR被映射到数据地址空间的0单元和1单元,TMS320C25可以通过指令进行访问并对其进行操作。TMS320C25以异步或同步的方式与外界通信。本文中,TMS320C25采用异步方式,以便有效地对TLC2543进行控制。其接口电路如图2所示。

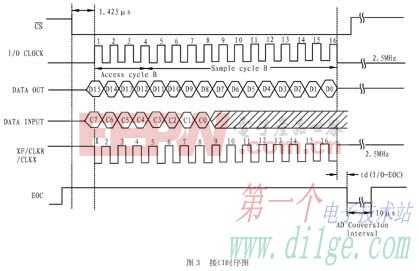

在图2中,TMS320C25使用40MHz晶振,指令周期为100ns。TMS320C25的DX连接到TLC2543的DATA INPUT,作为TLC2543的输入端。TLC2543的DATA OUT连接TMS320C25的DR,转换结果从该脚移入TMS320C25。XF是外部标志输出引脚,用于在系统中作为时钟源并由软件来产生时钟信号,最后将其接到TMS320C25的CLKX和CLKR,为TMS320C25的发送及接收操作提供时钟信号;同时,TLC2543的时钟信号也由XF引脚提供。值得注意的是:从接口的时序图中(见图3)可以看到,TMS320C25在下降沿时,数据保持稳定,而TLC2543是在上升沿接收输入数据因此,XF产生的时钟脉冲信号经非门74AHCT1G04后为TLC2543提供I/O CLOCK信号。

74ALS373的输入端是TLC2543的控制字,该控制字可以由拨码开关设定。控制字有8位,前4位(D7~D4)从11个模拟输入中选择一个进行转换或从三个内部自测电压中选择一个以对转换器进行校准。D3,D2用来选择数据长度,若转换器的分辨率为12位,内部转换结果也总是12位长。选择16位输出时,D3D2的值为11,TLC2543在转换结果的低位增加了4个被置为0的填充位,可以方便地与TMS320C25的16位串行接口通信。图2中,3-8译码器74ALS138的Y7接到74ALS373的OC端,74ALS373的端口地址为0X7,TMS320C25仅用一条IN指令即可将TLC2543的控制字读入。

74ALS138用来对外设地址译码。它的G2A与TMS320C25的IS引脚相连,当TMS320C25执行一条OUT指令时,外设地址放置在地址总线上,同时,IS为低,指明地址总线上的地址是I/O而不是外部数据或程序存储器。图2中,74ALS373的地址为0X7。当74ALS138的输出Y6触发D触发器74ALS74(外部地址为0X6)时,TLC25343的CS变低。74ALS138的Y5接到D触发器的CLR端,目的是保证在TMS320C25复位时,CS为高(复位时,地址线A0~A15均为低)。

接口的时序图如图3所示,在TLC2543的CS端变低到I/O CLOCK的第一个上升沿之间应有1.425μs的延时,以保证TLC2543内部电路正确地初始化。TMS320C25将读入字在I/O CLOCK的前8个时钟周期发送到TLC2543,后8个时钟传送的内容将被忽略。12位转换结果以左对齐的方式(最低4位为0)被TMS320C25接收。在访问周期B(ACCESS B)时,TLC2543选中需采样的通道;在采样周期B(SAMPLE B)对选中的通道进行采样。在I/O CLOCK的最后一个下降沿,EOC变低并开始转换,在大约10μs的时间之后,EOC重新变高,表示TLC2543转换完成。

2. 软件设计

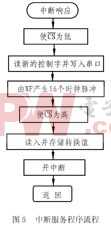

该软件由主程序和中断服务子程序两部分组成。主程序中完成TMS320C25的初始化,并把TMS320C25的串口初始化为无帧同步脉冲连续操作方式,在这种方式下,首先应发送一个帧同步脉冲以启动串行传输,在后续的操作中,将不用帧同步信号。具体的过程读者可以参考文献[1]或相关的资料。主程序初始化后,TMS320C25向TLC2543发送8位控制字,置TLC2543的CS为低,并由XF引脚提供16个脉冲,将TLC2543第一次转换的结果读入。主程序在最后进行定时器的初始化,使TMS320C25每隔0.2ms产生一次中断。当产生定时中断时,TMS320C25由一条B TINT跳转指令跳到中断服务子程序。在中断服务子程序中TMS320C25读入新的控制字,将其加载到DXR(数据发送寄存器)并从DX引脚发送,同时将前一次转换的结果从DR引脚移入并保存。编程时,使用NOP指令在XF引脚产生频率为2.5MHz的时钟脉冲。对TLC2543来说,必须提供正确的时钟个数,否则,采样就会失败。软件的流程图分别如图4和图5所示。

参考文献:

1.黄凤英.DSP原理及应用.东南大学出版社,1997.

2.TLC2543数据手册.武汉力源电子股份有限公司.

评论