FPGA通过以太网与PC机通信完整方案

一、简介

使用以太网接口实现PC和FPGA的通信,相对于串口而言,具有更高的传输速度。采用以太网接口的目的在于,在一定技术要求下,实现PC机和FPGA的实时数据传输。从而可以借助PC机强大的计算能力,降低FPGA的运算负担。

成都浩然电子有限公司开发的网络模块HS-NM5300A,作为实现以太网通信的主要元件。模块以韩国Wiznet公司开发W5300A为关键芯片。模块一端为RJ45,通过网络交叉线与PC机相连;另一端为外部总线,与FPGA的IO相连。模块内嵌10BaseT/100BaseTX的以太网物理层,支持自动握手功能,支持固件TCP/IP协议,通信理想速率可达到50Mbps。

W5300A接收PC机发来的数据包,进行协议解析,并将传输的数据保存在其内部寄存器中,或者将寄存器内的数据打包封装发送到以太网上。FPGA通过外部总线,访问W5300A的寄存器,从而对W5300A进行配置、查询数据包是否到来、收取/发送通信数据等等。

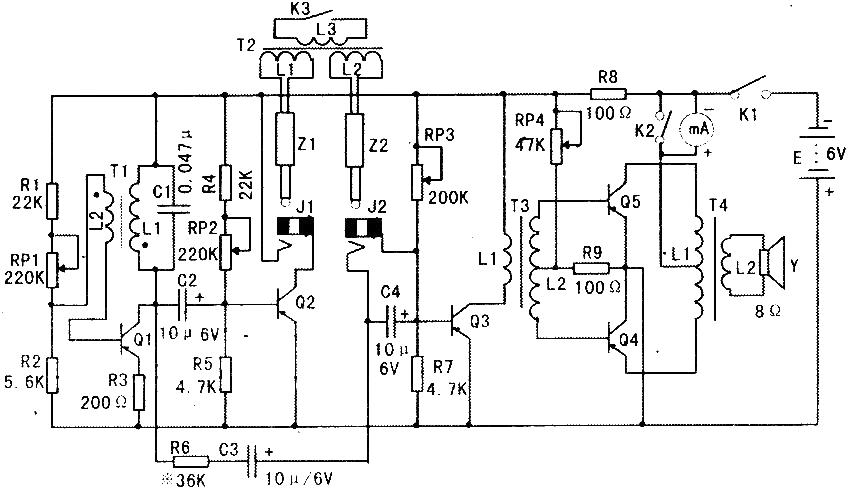

二、FPGA与W5300A的硬件连接

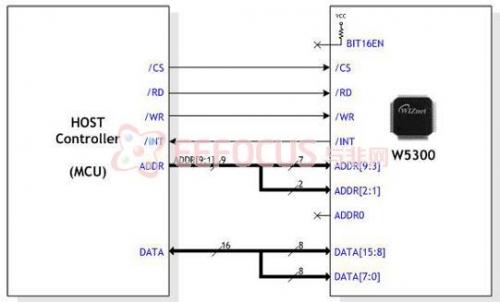

FPGA与W5300A的外部总线连接如下图所示(ref:W5300_v1.2.2_english,115-115)。

FPGA和W5300的连线,我们称之为外部总线。FPGA为外部总线的主机,W5300为从机。通过外部总线,可以实现FPGA对W5300的读/写。图中DATA为十六位数据线,ADDR为10位地址线,WR为写使能,RD为读使能,CS为片选使能,INT为中断请求。

三、外部总线的工作时序

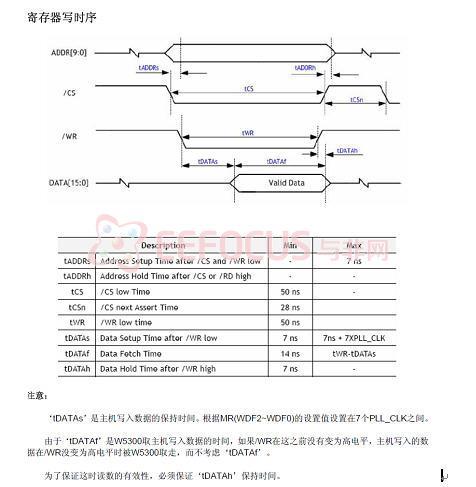

要使W5300正确读入/输出数据,外部总线上各信号电平应满足一定的时序要求。读时序如下图所示(ref:P120-122):

图中PLL_CLK为W5300A的内部时钟,频率为15OMHz。

四、FPGA程序实现

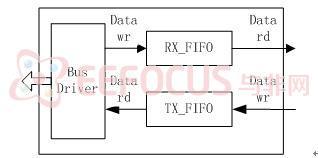

(1)FPGA网口通信模块的顶层结构如下图所示:

BusDriver是核心模块,驱动外部总线和RX_FIFO的写使能以及TX_FIFO的读使能。RX_FIFO和TX_FIFO是两个16位的先进先出存储器。在FPGA内部,可以通过读取RX_FIFO的数据,写TX_FIFO实现与以太网的数据交换。

(2)接口定义

|

引脚名称 |

IN/ OUT |

说明 |

有效状态 |

位置 |

|

Enet_ADDR |

OUT |

网络芯片总线的地址位 |

|

外 |

|

Enet_BRDY |

IN |

|

|

外 |

|

Enet_CSn |

OUT |

网络芯片总线的片选 |

低 |

外 |

|

Enet_DATA |

INOUT |

网络芯片总线的数据位,16位 |

|

外 |

|

Enet_INTn |

IN |

网络芯片总线的中断位 |

低 |

外 |

|

Enet_L_LINK |

IN |

网络电气连接位 |

高 |

外 |

|

Enet_RDn |

OUT |

网络芯片总线的读使能 |

低 |

外 |

|

Enet_RST |

OUT |

网络芯片硬件复位 |

高 |

外 |

|

Enet_WRn |

OUT |

网络芯片总线的写使能 |

低 |

外 |

|

RESET |

IN |

Bus_fifo模块的初始化,包括总线模块和FIFO |

低 |

内 |

|

rxfifo_dout |

OUT |

RX_FIFO的数据输出,16位 |

|

内 |

|

rxfifo_rd_en |

IN |

RX_FIFO的读使能,如果在rxfifo_empty_p为1,有可能出现错误。 |

高 |

内 |

|

rxfifo_empty_p |

OUT |

当RX_FIFO为空时,输出高电位 |

高 |

内 |

|

rxfifo_valid |

OUT |

在rxfifo_rd_en置1后一个fifo_clk置1,标示RX_FIFO输出数据有效。 |

高 |

内 |

|

txfifo_din |

IN |

TX_FIFO的数据输入,16位 |

|

内 |

|

txfifo_wr_en |

IN |

TX_FIFO的数据写使能 |

高 |

内 |

|

txfifo_full |

OUT |

当TX_FIFO满时,输出高电位 |

高 |

内 |

|

txfifo_valid |

OUT |

TX_FIFO数据输出有效位 |

高 |

内 |

|

fifo_clk |

IN |

RX_FIFO的读时钟和TX_FIFO的写时钟,上升沿从FIFO中读取或写入数据。10M |

升 |

内 |

|

CLK |

IN |

bus_driver的时钟,RX_FIFO的写时钟和TX_FIFO的读时钟。100M |

升 |

内 |

注:表中第五列“位置”,标示该信号线应连接至FPGA内部信号或者FPGA外部信号。

(3)TCP工作模式

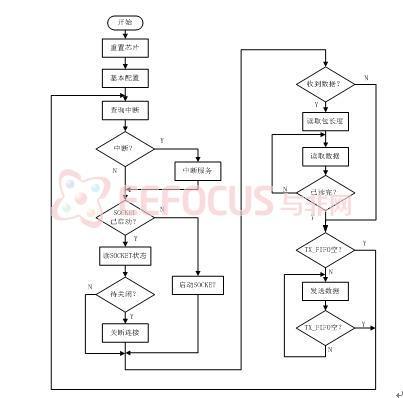

PC机与W5300A通信采用TCP协议。对于TCP模式,通信的一方根据IP地址和端口号与对端建立SOCKET连接。再通过指定的SOCKET发送和接收数据。建立SOCKET的连接有两种方式:“TCP服务器”和“TCP客户端”。区别在于谁首先发送连接请求(SYS数据包)。“TCP服务器”等待对端的连接请求,当收到连接请求时建立SOCKET连接(被动打开)。“TCP客户端”主动发出连接请求,与对端建立连接(主动打开)。出于方便考虑,由PC端发起连接,设定PC端为TCP客户端,W5300A为TCP服务端。通信流程如下图所示(ref:90)。

图中的LISTEN、ESTALISHED、CLOSED为对应SOCKET的状态。对W5300A的SOCKET正确地初始化(OPEN)后,SOCKET处于LISTEN状态,对网络进行侦听。当收到客户端发来的连接请求(SYS数据包),变为ESTABLISHED状态,此时客户端和服务器可以进行数据通信。当服务器断开连接或者收到客户端发来的断开请求(FIN数据包),W5300A相应的SOCKET状态变为CLOSED。服务器SOCKET更为详细的状态转换过程可以参考W5300A手册77页。

(4)busdriver模块的工作流程

busdriver通过外部总线对网络芯片进行复位和数据交换。通过访问W5300A的寄存器,实现网络芯片的配置、监控、数据收/发。同时,busdriver监视FIFO,如果RX_FIFO则暂缓收数;如果TX_FIFO不空则发送数据。Busdriver的工作流程如下图所示。

图中,重置芯片是指:对芯片硬件复位、软件复位;基本配置包括:配置 W5300A的MAC地址、IP地址、子网掩码、网关地址,分配W5300A的存储空间,中断设置等等。中断服务程序主要是读取芯片的中断寄存器,获取中断类型,并复位中断寄存器。值得注意的是,上图所示的流程是查询方式而不是中断方式。启动SOCKET的程序主要是:设置SOCKET端口号,工作模式(TCP服务器端),打开SOCKET、开始侦听等等。

(5)以太网通信的程序实现

考虑到处理器是FPGA,采用VHDL语言描述图中所示流程。与C语言顺序为执行不同,VHDL基于硬件结构、并发执行。图中用C语言可以很方便地描述出来,但是要在FPGA里面实现,则需要灵活运用状态机以控制其流程,且要尽力避免竞争和险象。限于正文篇幅,源程序在附录中给出。

评论