基于DSP与SJA1000的CAN总线系统设计方案

当前,有一些微处理器将CAN控制器嵌入到系统之中,但是仍有大量人们比较熟悉的微处理器并不带有CAN控制器。采用微处理器和CAN控制器组合的设计成为必要,而且,CAN控制器具有完成CAN总线通信协议所要求的全部必要功能,因此,CAN控制器与其它微处理器的接口设计成为设计CAN总线系统的首要工作。本文重点介绍以SHARC DSP为核心的、基于SJA1000的CAN总线接口设计。

SJA1000简介

SJA1000是一种独立的CAN控制器,用于移动目标和一般工业环境中的控制器局域网络(CAN)。它是Philips公司早期CAN控制器PCA82C200(Basic CAN)的替代品,而且增加了一种新的工作模式(PeliCAN),这种模式支持具有很多新功能的CAN2.0B协议。

SJA1000与微处理器的接口主要由8根数据和地址分时复用线完成:AD0"AD7、ALE/AS、、/E、、、MODE和,其中MODE为接口方式选择信号,可设置成Intel方式或Motorola方式。两者的区别在于:Intel模式下,处理器对SJA1000写时,用、作为读、写数据信号,ALE下降沿锁存地址(此时地址信号要保证基本的建立保持时间),仅在读、写数据时为低;Motorola模式下,读、写信号用区分(高电平读、低电平写),用/E选通数据(下降沿锁存),AS和CS类似于Intel的ALE和。目前流行的MCS51/96系列单片机提供了方便快捷的直接Intel方式接口,出于普遍性的考虑,本文以下的接口设计都是基于Intel模式的。

DSP的接口信号和时序

与早期的处理器不同,DSP芯片的片外引脚都采用地址线和数据线分离的设计方法,不再使用地址数据分时复用线,也没有ALE信号,这样就给CAN控制器与DSP的接口带来一定困难,且不同的DSP外部引脚和时序也略有区别。要设计CAN控制器与DSP的接口,首先必须比较DSP与CAN控制器的时序。

本文选用的DSP为ADSP21062,主频为40MHz,单周期(零等待)访问存储器时,要求存储器的响应(读或写)周期小于17ns,但许多存储器或外设的响应速度没有这么快,于是就要通过加等待来延长访问时间。ADSP2106x支持两种等待方式,即内等待(软等待)和外等待(硬等待)。

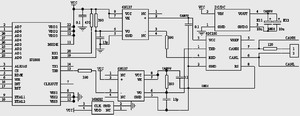

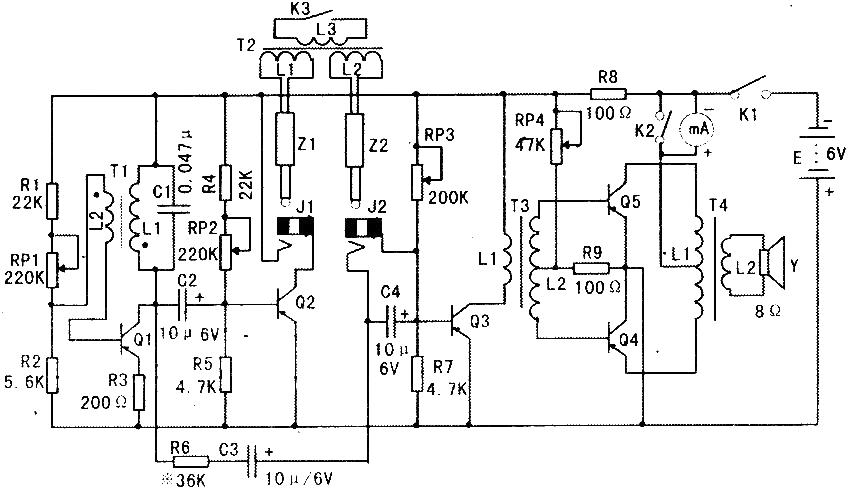

SJA1000和CAN总线的连接

选择82C250作为收发器,选择6N137高速光电隔离器实现系统和CAN总线的隔离。其连接方法如图1所示。这种设计既能做好电气隔离,又能保证数据的传输速度。

图1 SJA1000和CAN总线的连接

CAN控制器与DSP的接口设计方法

SJA1000的数据和地址信号为分时复用,而DSP为数据、地址信号分离的结构,而且DSP不提供ALE信号,设计的关键就是DSP要把SJA1000的地址当成数据写入并同时产生ALE信号。分析读写信号所要求的最短有效时间,由于读低电平到数据有效的时间最长为50ns,所以要保证读信号有效时间至少50ns,ADSP21062在用2个软等待时,其低电平时间为62.5ns(25ns/2+2×25ns),刚好能满足要求。

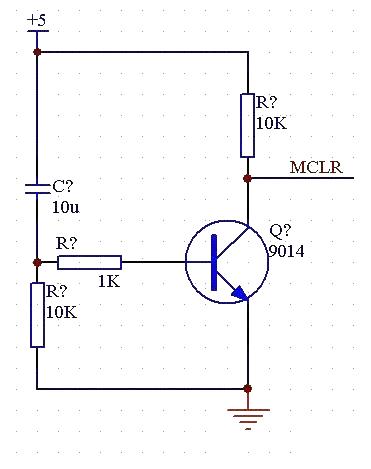

ADSP21062和SJA1000接口的简化设计

在外围设备连接不多的情况下,接口电路可以使用几个逻辑门实现。由于访问外部数据时,数据总线的低16位未用,所以使用的数据线从DATA16起始。当Flag1=1时,SJA1000的WR始终为1,其ALE为DSP的WR的反向,当DSP把地址当成数据写入SJA1000时,低电平DSP的WR信号会转换成高电平的ALE,并在ALE的下降沿把数据锁存。当Flag1=0时,ALE始终为0,无地址锁存操作。SJA1000的WR直接受DSP的WR信号控制。由Flag2直接控制CS。其连接如图2所示。

ADSP21062和SJA1000简化接口设计的相应程序如下:

1) #define CANADDR 0x400000

2) bit set mode2 FLG1O|FLG2O;

//设置Flag1,Flag2为输出

3) r1=0x00047800; dm(SYSCON)=r0;

//设置外部空间大小

4) r0=0x21a8c429;dm (WAIT)=r0;

//用2个软等待访问MS0

5) bit set astat ASTAT_FLG1;

//Flag1=1,

6) r0=addr;dm(CANADDR)=r0;//写入要访问的SJA1000的内部地址

7) bit clr astat ASTAT_FLG1;

//Flag1=0

8) bit clrastat ASTAT_FLG2;

//Flag2=0,CS=0

9) i0=CANADDR;r0=dm(i0,0);

//读取SJA1000相应地址的数据

10) r1=3;dm(i0,0)=r1;

//写入数据到SJA1000相应地址

11) bit set astat ASTAT_FLG2;

//Flag2=1,CS=1,5

为说明方便,对各条指令编号。运行指令5、7、8、11各花费25ns,运行指令6、9、10各花费100ns,所以完成一次读或写需300ns。

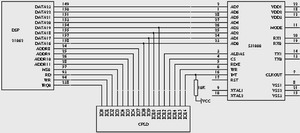

基于CPLD的ADSP21062和SJA1000接口设计

在连接多个外围设备时,其译码电路比较复杂,可以使用CPLD完成逻辑译码控制。利用地址数据信号产生CAN的ALE、CS等信号。其优点在于使用多个总线设备时,可用一片CPLD完成所有总线设备的译码,这种方法有更好的适用性。其连接方法如图3所示。

图3 基于CPLD的ADSP21062和SJA1000设计图

DSP的程序设计如下:

1) #define CANNCS 0x400100

//清CANCS的地址,对此地址操作使CAN的CS无效

2) #define CANCS 0x400200//置CANCS的地址,对此地址操作使CAN的CS有效

3) #define CANALE 0x400500

//置CANALE的地址,对此地址操作使CAN的ALE可变化

4) #define CANNALE 0x400600

//清CANALE的地址,对此地址操作使CAN的ALE恒为低

5) #define CANRW 0x400900

//对此地址操作完成CAN数据的读、写

6) r1=0x00047800; dm(SYSCON)=r0;//设置外部空间大小

7) r0=0x21a8c429;dm (WAIT)=r0;

//用2个软等待访问MS0

8) r7=0x07;dm(CANALE)=r7;

//ALEhigh=1,CANALE为CANWE的取反

9) r4=addr;dm(CANRW)=r4;

//写入要访问的SJA1000的内部寄存器空间地址

10) r7=dm(CANNALE);

//ALEhigh=0,CANALE总为0

11) r7=0x07;dm(CANCS)=r7;

//CANCS=0

12) r3=dm(CANRW);

//读取SJA1000相应地址的数据

13) r1=3;dm(CANRW)=r1;

//写入数据到SJA1000相应地址

14) r7=dm(CANNCS);

//CANCS=1

运行指令8、9、11、13各花费100ns,运行指令10、12、14各花费75ns,所以完成一次读或写需525ns。速度比前文的简化设计要慢一点,但这种设计更利于扩展,适合于多个外设接口,同时节省了两个Flag引脚。当SJA1000工作在最大传输速度1Mbit/s时,由于在一个数据帧中会插入约42bit其它帧信号,所以完成8bit传输的时间约为50s。前两种设计的速度分别是其167倍和95倍。所以这两种设计都能满足SJA1000的传输速度要求。

CPLD程序设计

图4 CPLD的逻辑图

图4中,用74138进行译码,生成ALE、CS等信号。当执行指令6时,设置了外部空间的大小,在访问地址0x400000~0x4fffff时会使能MS0,74138的G2AN将有效。当地址A11"A8=0001,Y1N=0,CANCS的清零由DSP的RD控制,RD信号的低电平将使CANCS=0,指令11完成此功能。当地址A11"A8=0010,数据D19"D16=1000,则Y2N=0,DSP的WR信号的将使CANCS=1,指令14完成此功能;当地址A11"A8=0101,数据D19"D16=0111,则Y5N=0,DSP的WR信号沿将使ALEhigh=1,此时CANWE始终保持1,CANALE为WR取反,指令8完成此功能;当地址A11"A8=0110,则Y6N=0,RD信号的低电平将使ALEhigh=0,此时CANALE始终保持0,CANWE为WR,指令10完成此功能。

ADSP21062仅有3个外部中断,在挂多个外设时就显得资源紧张。图4中,低电平有效或下降沿有效的中断信号可以用与的关系连接到一个中断上,DSP在响应中断后,读相应的多个外设,判断是来自哪一个外设,这样就可以扩展更多的中断。

结语

SJA1000接口为地址/数据复用模式,DSP处理器通常为地址/数据总线分离的结构,本文提供了两种不同接口的思路和方法。测试表明,这种方法确实可行,传输效率高。

评论