高速DSP与串行A/D转换器TLC2558接口的设计

摘 要:根据高速定点DSP芯片TMS320F206的特点,提出使用串行A/D转换器TLC2558作为DSP系统的模拟量输入部分,解决了以往基于并行数据传输的A/D转换器不能与高速DSP进行很好配合的问题。在此基础上设计了DSP与串行A/D转换器连接的硬件电路,并就A/D转换在软件设计时应注意的问题进行了探讨。

DSP(Digital Signal Processor)芯片与单片机相比,具有运算速度更快、功能更强的特点,它自诞生以来在工业控制领域的应用越来越广泛。随着DSP芯片应用的普及,DSP处理速度快的特点使它在与普通A/D转换器接口时遇上了困难,使普通的、以并行接口传输数据的A/D转换器与DSP接口时出现读数不可靠的问题。为此,需要利用DSP芯片的其它接口资源作为A/D转换数据的输入。

1 芯片简介

1.1 TMS320F206

TMS320F206是TI公司TMS320C2xx系列16位高速定点DSP芯片,具有先进的哈佛结构,采用流水线操作和高度专业化的指令系统,集成了片内外围设备和片内存储器。当采用20MHz晶振作为时钟源时,它的主时钟周期为50ns。F206芯片具有一个同步串行口,它能提供与编译码器、串行A/D转换器等串行器件的直接通信。在20MHz的时钟下,发送和接收操作的最大传输速率是10Mbit/s,并有四级深度的发送和接收FIFO缓冲器,在与同步串行口相关的引脚中,DX为发送串行数据引脚;FSX是帧同步信号,用来启动传送(数据帧的开始);CLKX为发送时钟信号,定时进行位传送。同步串行口接收部分对应的引脚相应为DR、FSR和CLKR。

1.2 TLC2558

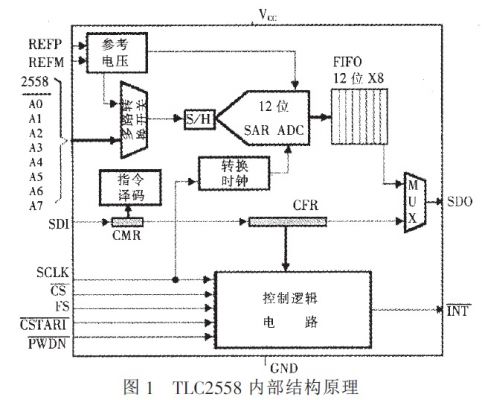

TLC2558也是TI公司生产的高性能12位串行模数转换器,共有8路模拟通道,最大采样率为400ksps,自带有8级FIFO,输入模拟量电压在0~5V之间。TLC2558的内部结构原理如图1所示。由图1可见,TLC2558由控制逻辑电路、A/D转换器、多路转换开关和采样/保持器、参考电压、FIFO、配置寄存器(CFR)和命令寄存器(CMR)等部分构成。配置寄存器(CFR)用来设定TLC2558的工作方式,它和外部的控制信号一起可以有效地控制芯片的工作,包括采样、转换、读取数据等;命令寄存器CMR用来选择模拟量输入通道和读写CFR。在外接的信号中,SCLK引脚接时钟信号,芯片通过引脚SDI在SCLK时钟的下降沿接收数据,通过引脚SDO在SCLK时钟的上升沿传送数据;CS/为片选信号;FS为DSP帧同步输入,表示串行数据帧开始输入或输出;在扩展采样时,CSTART/可用来控制模拟输入采样的开始:高电平到低电平的跳变开始模拟输入信号的采样,而低电平到高电平的跳变则置S/H为保持模式并启动转换,如不用,可将此引脚接正电源;PWDN/为逻辑零时,模拟及基准电路均断电,使芯片低功耗运行。INT/可设定为主处理器的终端输出信号,INT/的下降沿表示数据已转换完毕,请求CPU接收数据。AD转换器采用12位的逐次逼近的ADC。TLC2558片内还包含了一个8级12位的FIFO缓冲器,数据转换完后,放入FIFO中等待主处理器读取数据,使用者能够根据需要通过配置CFR选择FIFO中数据满2个、4个、6个、8个时或不经过FIFO,由CPU读取,这样可以使用户根据需要灵活选择DSP读取数据的方式。

2 硬件设计

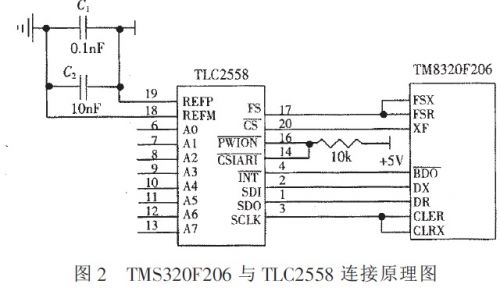

在分析了F206同步串行口和串行A/D转换器TLC2558外接信号的特点后,可以利用TLC2558能与F206的同步串行口进行无缝连接的特点,在F206的同步时钟信号的作用下完成A/D转换数据的传输。图2是F206的同步串行口与TLC2558的硬件接口原理图。图中,A/D转换器的A0~A7为模拟量输入端,REFP与REFM分别接5V正电源和5V地线,使A/D模拟量输入范围为0~5V;FS接F206同步串行口的FSX和FSR,使数据输入和输出的帧脉冲信号均由DSP产生;FSX和FSR相连使DSP的输入帧脉冲和输出帧脉冲不再独立,保证同步串行口数据的发送接收操作以相同的帧时钟进行;SCLK接F206的CLKR和CLKX,这样,数据输入和输出的同步时钟信号均来自DSP;SDI和SDO分别接DSP同步串口信号输出、输入脚DX、DR,其中,SDI引脚用来接收DSP发送的命令,并写入命令寄存器CMR和配置寄存器CFR,设定A/D转换器的工作方式和采样通道;CS/接DSP的XF,此时,XF相当于具有闭锁功能的输出脚,正常时为高电平,当需要对A/D进行读/写信息时,使XF输出低电平,选中A/D,然后再对A/D进行操作;INT/接DSP的BIO/,当TLC2558的FIFO中已转换的数据达到规定数量时,芯片发中断信号(INT/变低)通知DSP读取数据,这样,DSP就能以查询方式检测到BIO/为低电平,然后读取数据。

通过对TLC2558的配置寄存器CFR进行写操作,可以选择A/D转换的转换方式,TLC2558共有四种转换方式:(1)单次模式,它是唯一不用FIFO的模式,每采样一次,就必须读取数据;(2)重复模式,即反复对一固定输入端进行采样、转换,存入FIFO中的结果到设定的数量后,读取这些数据,然后开始新一轮的采样、转换;(3)扫描模式,它是对选中的通道依次进行采样、转换,当FIFO放置的数据达到规定值后,扫描方式结束,在启动下一次扫描之前,CPU必须读取FIFO中的数据;(4)重复扫描模式,即重复模式和扫描模式的综合,工作方式与扫描模式相似,当FIFO数据中的数据达到规定后,和重复模式一样去读取数据。扫描模式由于只要对TLC2558写一次命令就可以完成所有通道的采样和转换,所以用时最少,是转换效率最高的方式,因此,对于要求采集模拟量较多、速度要求较高的场合,采用扫描模式是理想的选择。而对于采集模拟量较少或者速度要求不是很高的时候,可以选择便于编程和调试的单次模式。

3 TLC2558工作时序分析

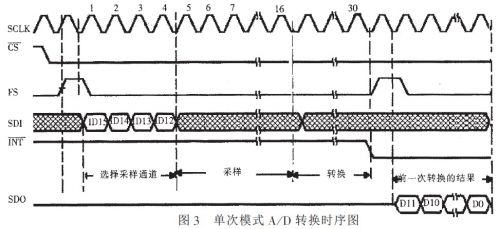

TLC2558是以DSP的同步时钟脉冲CLKX和CLKR为基准进行数据的发送和接收的,当采样频率为600Hz时,采用单次模式就可以达到要求的速度,以单次模式为例,对某个通道进行A/D转换时,首先要通过命令寄存器选择该通道,由于命令寄存器是一个4位的寄存器,所以需要4个同步时钟周期(SCLK),采样一次需要12个SCLK,转换一个模拟量需要14个SCLK,因此,完成一次转换共需要30个SCLK。当DSP采用202MHz晶振作为时钟源时,同步串行口的时钟周期是主时钟周斯的两倍,即100ns。所以,采用单次模式时完成一次采样/转换总共需要3us。图3是单次模式下A/D转换的时序,由图可见,在同步时钟和帧脉冲的作用下,A/D转换器通过SDI和SDO接收和发送数据。

4 编程时应注意的问题

由于TLC2558在上电或从低功耗方式重新启动后第一次转换的数据是无效数据,所以,造成了此后每次转换完成后从SDO读出的不是当次转换的数据,而是前一次的数据,如图3中的SDO所示。为了在程序执行中,在每个采样中断周期内都能得到正确的数据,可以采用以下措施:当要对通道0~通道n(n≤7)进行转换时,在每个中断周期内,依次对通道0~通道n采样和转换后,再对通道0进行一次采样和转换。每次转换完成后,读出的是前一个通道的转换数据,因此,对通道1~n采样完成后,读出的是通道0~n-1的数据,而当最后对通道0的采样完成后,读出的是通道n的数据。通过这种方式,使DSP能在每个采样周期内都能正确读出各通道A/D转换的数据。

5 结束语

本文简单介绍了串行A/D转换器TLC2558的工作原理及高速DSP进行接口的设计。DSP通过其同步串行口接收A/D转换的数据,解决了以往DSP不能与并行接口A/D转换器很好连接的问题。同时,就设计A/D转换程序的过程中要注意的问题作了说明。

评论