浅谈spartan-3系列FPGA配置电路设计方案

这里要谈的时xilinx($233.7100)的spartan-3系列FPGA的配置电路。这里要列出一个市面上最常见的spartan-3的xc3s400($17.3600)的配置电路,所有spartan-3的FPGA配置电路的链接方式都是一样的。xc3s400($17.3600)是40万门FPGA,它的ConfigurationBitstream虽然只有1.699136Mbit,但是它还是需要2Mbit的配置芯片XCF02S($4.1895),不能想当然的以为我的设计简单,最多用到1Mbit,那么我选XCF01S($3.1255)(1Mbit)就可以了。事实并非如此,即使你只是用xc3s400($17.3600)做一个流水灯的设计,那么你下载到 ROM(XCF02S($4.1895))里的数据也是1.699136Mbit的,所以对于FPGA的配置ROM的选择宜大不宜小。

配置电路无非有下面五种:主串,从串,主并,从并,JTAG。前四种是相对于下载到PROM而言的(串并是相对于不同配置芯片是串口和时并口协议和FPGA通讯区分的),只有JTAG是相对于调试是将配置下载到FPGA的RAM而言的(掉电后丢失)。FPGA和CPLD相比,CPLD是基于 ROM型的,就是在数据下载到CPLD上,掉电后不丢失。而FPGA则是基于RAM的,如果没有外部ROM存储配置数据,那么掉电后就丢失数据。所以 FPGA都需要外接有配置芯片(当然现在也有基于FLASH($44.9500)的FPGA出现)。那么我们就来看一下主串模式下FPGA的配置电路的连接。

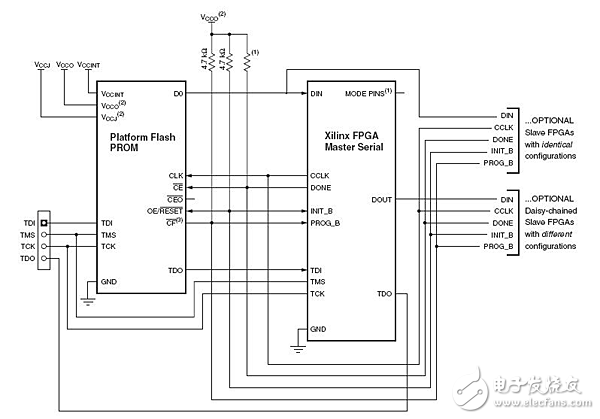

官方的硬件连接如下:

为了增加配置电路的可靠性,通常我们我们增加一些抗干扰的设计(如增加滤波电容、匹配电阻):

先看PROM芯片的各个管脚吧。根据datasheet给供相对应的电平;3脚CLK是接了FPGA的CCLK,数据通信的同步就是通过FPGA的CCLK产生的时钟进行的;因为使用的芯片时串行的配置芯片,所以只有一个数据信号口DO,连接到FPGA的DIN口,和上面的时钟信号协同工作完成串行数据传输,每当CLK的上升沿锁存数据,同时PROM内部的地址计数器自动增加;另外还有两条控制信号线时INIT(连接PROM的OE/RESET)和DONE(连接PROM的CE),OE/RESET是为了确保每次重新配置前PROM的地址计数器复位;关于CE脚,官方资料说得也不是很详细,以我个人的理解,CE应该是chip enable的缩写,从它和FPGA的DONE脚连接我们不难推断出,FPGA未配置完成时DONE=0,那么配置芯片PROM处于片选状态,而一旦配置完成DONE=1,那么PROM就不再被选通,同时datasheet也说到这个管脚可以直接接地,就是一直片选中,但是这样会使DATA口有持续的数据信号输出,同时导致不必要的电流消耗;CEO脚这里不接,因为它在多个PROM的配置电路中时作为下一个PROM的OE端信号连接用的;CF信号时连接 FPAG的PROG_B接口的,它的作用就是产生开始配置信号,它连接了一个上拉电阻,如果PROG_B产生低电平脉冲则PROM会重新开始一次配置,所以我们会在这条线上接一个按键到地,如果按键按下那么就会使能PROM重新配置FPGA;还有几个信号接口TDI,TCK,TMS,TDO都是PROM和 PC连接的信号,PC通过这些电路下载数据到PROM中。

上面谈及PROM的信号接口时都附带的谈到了FPGA的配置管脚。这里再做一些归纳性的说明。FPGA有7个专用的配置管脚,4个专用的JTAG管脚(TDI,TCK,TMS,TDO),这些管脚是由VCCAUX专门供电的(该系列FPGA通常接VCCAUX=2.5V)。FPGA的M0,M1,M2脚是进行配置模式选择用的,该电路主串模式下{M0,M1,M2}=000,如果时JTAG下载模式{M0,M1,M2}=101。上面没有提及的HSWAP_EN管脚接地,则是用于设置当 FPAG处于配置状态下其它闲置管脚为上拉状态,而如果该管脚接高电平,则FPAG处于配置状态下其它闲置管脚浮空。所以为了减少FPGA配置过程的干扰,一般把此脚接地。

评论