基于Nios Ⅱ嵌入式软核多处理器系统研究

0 引言

基于SoPC 技术开发的嵌入式Nios Ⅱ软核多处理器系统具有可自主设计,重构性好,软硬件裁剪容易,系统扩充升级方便,能兼顾性能、体积、功耗、成本、可靠性等方面的要求。研发嵌入式Nios Ⅱ软核多处理器系统,是提高嵌入式系统性价比和实用性一种有效途径。

1 片上Nios Ⅱ嵌入式软核多处理器系统

嵌入式系统的核心是RISC 处理器,具有代表性的RISC软核处理器是Nios Ⅱ处理器。软核处理器是指用编程的方法生成的处理器。是一种将硬件逻辑、智能算法、硬件描述语言和编程有机的结合出来,设计处理器硬件电路的新技术。

片上Nios Ⅱ嵌入式多处理器系统优势在于设计者可根据的实际的需要,自主选择Nios Ⅱ处理器的类型和数目并进行设置,对存储器和外围设备进行优化配置,最大限度提高片内资源和系统资源的利用率。

1.1 Nios Ⅱ处理器

由Nios Ⅱ软核处理器构建的系统,对系统软硬件容易进行裁剪,并可集成在一个FPGA 芯片上,构建系统和实时评估非常迅速、方便,可大大地缩短设计周期,降低设计风险。

1.2 多处理器系统类型

按共享资源分为非共享资源多处理器系统和共享资源多处理器系统两种。非共享资源多个处理器系统中的多个Nios Ⅱ处理器完全是独立的,不共享系统资源,处理器相互之间无干扰,系统结构不太复杂。共享资源多处理器系统在共享资源的情况下,要确保多个Nios Ⅱ处理器安全、可靠的工作,它对提高每个处理器的性能、减小体积,降低成本和功耗有利,但系统软件的设计较为复杂。

按处理器拓扑结构分为2 种,一种是非层次结构,处理器与系统组件的连接容易;另一种是层次结构,它可根据实际需要来确定Nios Ⅱ处理器的数目,优化系统的内部结构,有效利用FPGA芯片的资源。但存在平衡多处理器的负载和任务协调的问题。

2 共享资源多处理器系统

由多个Nios Ⅱ软核处理器,一套片上外设接口,片上存储器,片外存储器接口等并集成在一个FPGA芯片上,构成片上嵌入式Nios Ⅱ软核多处理器系统的基本架构。

2.1 共享系统资源

Nios Ⅱ多处理器系统可共享存储器、外围设备系统资源。为了确保每个处理器共享资源,防止由于处理器之间的干扰,引起程序或数据的错误,导致整个系统的崩溃。Nios Ⅱ多处理器系统中使用硬件互斥核组件对共享资源进行保护处理,以协调各个处理器的正常工作,确保处理器之间不受干扰,从而提高多处理器系统的性能。

2.2 硬件互斥核

用硬件互斥核来协调各个处理器对共享资源的访问。硬件互斥核是没有内部功能的,是一个简单的QSYS组件。它提供了一个协议来保证对共享资源的所有权的互斥,互斥协议是在任何时刻只有一个处理器允许访问共享硬件资源,这样才能有效保护多个处理器访问使用硬件资源,防止数据的损坏或系统的崩溃。互斥核mutex提供一个原子的测试和设置操作,它允许处理器测试,如果互斥是可用的话,获得互斥锁处理器进行单一的操作。当处理器完成使用共享外设与互斥锁,会释放互斥锁。此后,另一个处理器可以获取该互斥锁和共享外设的使用权。

需要注意,互斥核并没有外设系统被多个处理器同时访问的物理保护,运行在处理器上的软件负责遵守互斥协议,软件通过写获取互斥锁后,处理器访问其相关联的共享外围设备。多个处理器访问一个mutex核,则每个处理器有一个唯一的标识符ID(cpuid)。Altera提供了Nios Ⅱ处理器访问硬件的子程序,这些函数是针对mutex 核的,直接对底层硬件进行操作,每个处理器通过写它的cpuid 控制寄存器的值到mutex 寄存器的owner 域对mutex 加锁,而mutex 不能对HAL API 或ANSI C标准库进行访问。

3 片上嵌入式Nios Ⅱ软核六处理器系统实例

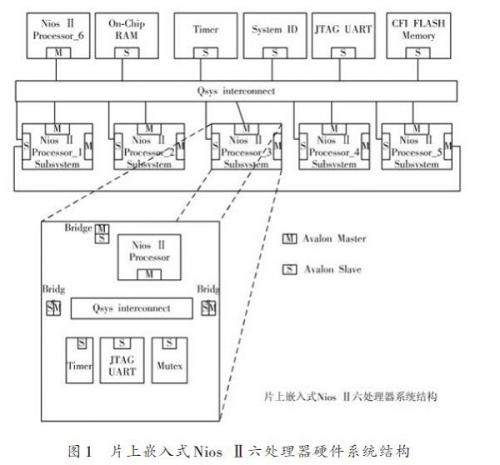

片上嵌入式Nios Ⅱ六处理器硬件系统结构示意图如图1所示。

3.1 硬件系统结构

由六个Nios Ⅱ处理器、硬件互斥核、片上存储器、JTAG UART、定时器、FLASH 控制器、FLASH 存储器、System ID、Avalon Switch Fabric总线组成系统硬件的基本结构。该系统采用层次结构,其中第六个Nios Ⅱ处理器、片上存储器、JTAG UART、System ID、定时器、FLASH 控制和存储器处在结构的顶层。处在底层的5 个子系统共享存储器资源,每个子系统包含一个NiosⅡ处理器、JTAG UART、定时器和硬件互斥核,用Ava-lon-MM、Pipeline Bridges将逻辑相邻的子系统处理器和互斥核之间连接成一个环,连接子系统与系统顶层组件之间的通信通道。

3.2 Nios Ⅱ处理器选择和参数设置

Nios Ⅱ处理器有快速型、标准型和经济型三种类型[3],快速型配置性能最高,经济型配置占用片内资源最少,标准型配置的性能和占用片上资源介于快速型和经济型之间。根据实际应用需要对系统性价比及功耗的要求,合理选择和配置Nios Ⅱ处理器。

多处理器系统中对每一个处理器都要进行正确的设置,否则即使创建的硬件系统已通过编译并生成,也会造成多处理器系统不能正常运行的问题。如果多个处理器使用片上存储器为共享程序存储器,则必须正确设计异常地址。如果使用CFI FLASH存储器区域作为多个处理器的引导区,则必须要正确设计复位地址。使用不同类型的存储器要正确的进行设置。

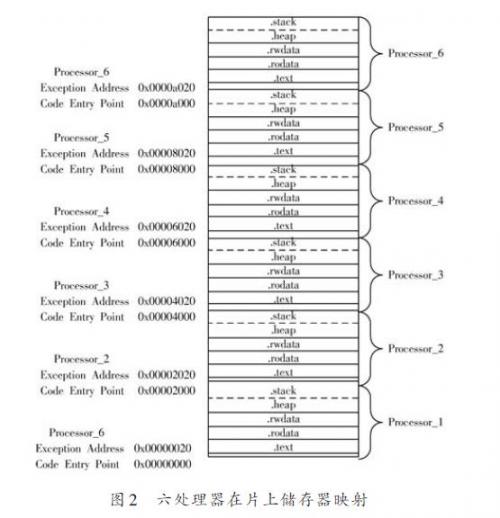

3.3 共享程序存储器

为了降低成本、功耗,简化多处理器系统结构,实例中利用FPGA的芯片资源共享程序存储器,六个Nios Ⅱ处理器的运行软件共同使用片上存储器,每个处理器的软件位于片上存储器所属特有的存储器区域。如果六个处理器的软件在片上存储器运行,假设每个处理器的软件需要有8 KB的内存空间用于程序代码和数据。这样第一个处理器使用片上存储器0×0~0x1FFF之间的作为其程序空间,第二个处理器使用片上存储器0×2000~0x3FFF 之间的区域,第三个处理器使用片上存储器0×4000~0x5FFF之间的区域;其他各个处理器所需的存储器区域采用同样的方法对片上存储器进行分区。

Nios Ⅱ SBT 提供了一个简单的存储器分区模式,允许多个处理器的软件运行于同一存储器的不同区域,确保位于存储器中的主要代码段的链接和固定地址。

图2所示六个处理器在片上储存器的分区及代码段的链接。

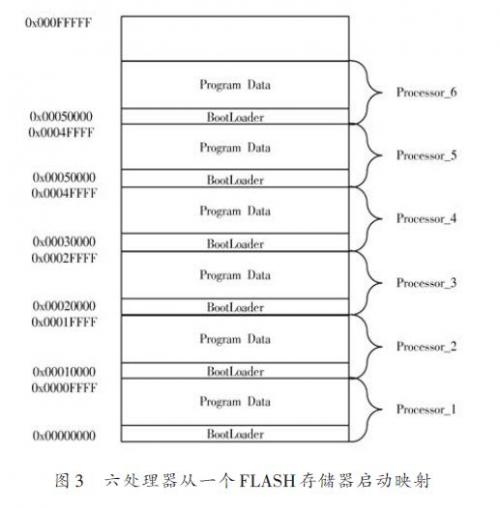

3.4 设置启动地址

在多处理器系统中,每个处理器在存储器中必须拥有自己的启动区域,多个处理器不能从同一非易失性存储器的同一地址启动。启动存储器类似程序存储器一样也可以进行分区,但段和链接的概念不同,因为通常引导代码只是复制到它实际的程序代码被链接在RAM中,然后跳转到该程序代码处。为了从同一非易失性存储器的不同区域启动多个处理器,设置每个处理器复位地址,这个地址就是启动该处理器的位置,启动区域要留出足够的空间存放启动代码。由于没有支持机制多个处理器无法直接访问CFI FLASH存储器,需要使用一个CFI FLASH控制器,Nios Ⅱ处理器通过CFI FLASH控制器读取或写入到CFI FLASH存储器。如果多个Nios Ⅱ处理器启动在同一个CFI FLASH存储器。为确保安全访问,必须删除一个主控处理器之外的CFI FLASH 存储器alt_main()函数所有初始化的驱动程序,并确认启动前完成所有其他处理器在CFIFLASH存储器的程序初始化。图3所示六个处理器从一个FLASH存储器启动的映射。

3.5 共享外设资源

多个处理器共享外设存在严重的问题。共享外设的最大的问题是中断,如果允许一个外设中断且所有处理器共享它,没有可靠的方法保证哪一个处理器首先响应中断且为哪个外设服务。此外,如果外设是用来作为多处理器的输入设备,很难确定哪个处理器应该从设备中接受输入信息。Nios Ⅱ多处理器系统共享外设资源的方式,是系统中的外设仅被一个处理器访问,如果其他处理器需要使用外设,最好是使用硬件先进先出(FIFO)或消息缓冲区互斥保护。创建多处理器系统时,仅对需要通信的处理器和外设之间进行连接。例如,如果一个处理器运行仅使用一个片上存储器,该处理器没有必要与系统中任何其他存储器连接。处理器与存储器的分离,不使用物理断开连接,这样可节约FPGA资源,保证处理器不会破坏存储器的数据。

共享资源多处理器与各种组件连接是设计中的关键环节,要验证每个处理器及所需组件的连接是否正确。多数组件最好是由单一的处理器管理。例如处理器A要求一个外设的服务,而该外设与处理器B连接并由处理器B 管理,处理器A 要求对该外设进行操作,处理器A 必须请求处理器B.这样可以使用处理器互斥保护的共享片上存储器,用于个两处理器之间的通信,达到多处理器共享外设的目的。

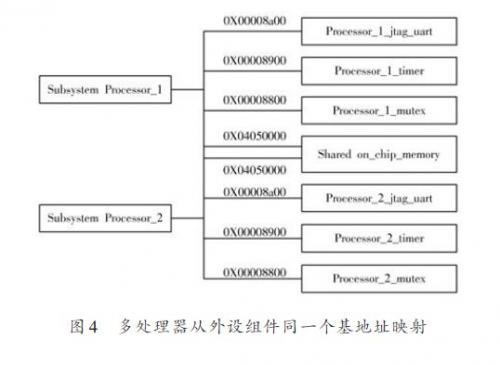

在多处理器系统中,每个从外设可以占据相同的基地址不会发生冲突,只要每个外设是被不同的处理器控制。因为每个从外设不必一定被每个处理器控制。如果处理器A被连接到映射地址为0x00008a00的一个从外设,处理器B也可以被连接到映射地址0x00008a00另一个从外设,只要处理器A是没有连接到处理器B的从外设,处理器B 没有连接到处理器A 的从外设,不会因为从外设占据相同的基地址而发生冲突。图4方框图显示多处理器系统中不同的从外设组件映射到同一个基地址的示例。

4 系统调试及软件设计

Nios Ⅱ SBT for Eclipse 工具包括了许多功能,它可以进行Nios Ⅱ多处理器系统的软件开发。能同时对多个Nios Ⅱ处理器进行调试会话,也可单独暂停和恢复每个处理器的运行,单独设置每处理器的断点。如果一个处理器遇到一个断点,它不会停止或影响其他处理器的操作。Nios Ⅱ SBT for Eclips对多个处理器系统具有可同时进行在片调试的能力。

系统软件设计应注意的问题,在设计Nios Ⅱ多处理器系统的软件时,必须要考虑系统硬件结构的特点以及启动地址和异常地址的设置。设计调试运行多处理器系统软件与单处理器系统相似,一定要清楚每个处理器的复位地址、异常地址,CPUID寄存器的值以及存储器的类型。多个处理器使用同一个程序存储器,而每个处理器的程序必须存放在不同的区域,用异常地址为每个处理器存放程序确定内存区域,使用QSYS为每个处理器设置异常地址。

5 结语

SoPC技术的出现带来全新的嵌入式处理器硬件的设计理念,使得设计嵌入多处理系统硬件电路的有了多种方法和途径。实例Nios Ⅱ嵌入式软核六处理器系统的方案具有一定可行性和实用性。如何提高嵌入式多个处理器系统的效率,实现资源的最佳配置,简化系统结构、降低成本和功耗,怎样合理选择时钟、I/O、其他外设等问题有待进一步研究解决。

评论