采用集成DSP与微处理器内核的嵌入式系统应用

嵌入式应用包括信号处理算法与控制算法,在多种实时嵌入式系统中,这两种算法共同执行必需的功能,因此我们应了解控制算法与数字信号处理器 (DSP) 算法是如何实现互操作性的。在手机和 MP3 播放器等应用中,要解决上述互操作性问题,传统做法是分别用 RISC 处理器和DSP来处理控制算法与信号处理算法。例如,在手机中,信号处理功能负责处理音视频应用中的回声消除与编解码工作。由于DSP 架构是专门设计用于执行信号处理算法的,因此信号处理算法在 DSP 上的 运行效率很高;而手机中的控制软件则负责执行状态机,即控制用户界面、键盘及其它非信号处理功能。

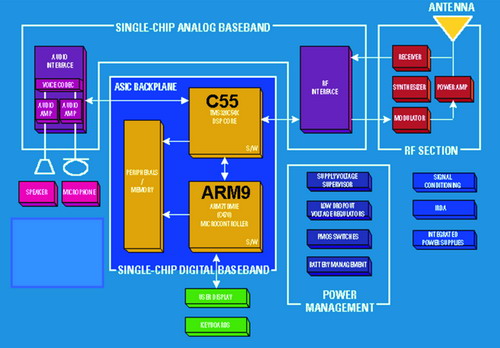

开发包括信号处理与控制算法且要求这两种算法间实现互操作性的嵌入式应用时,我们要面临几大挑战。举例来说,当我们将桌面应用或其它复杂应用连接到嵌入式设备上时,让该嵌入式设备的DSP/RISC 内核实时工作并适当地进行代码分组(code partitioning)会相当困难,因为要这两种不同内核实现同步操作需要进行大量的工作。视频或协议处理等众多高级嵌入式应用会增加多内核上代码分组的难度,而且大多数代码分组工作都要由编程人员完成。以采用德州仪器 (TI)TMS320C55x DSP 与 ARM RISC 处理器的双内核架构为例来说,DSP 执行信号处理任务,而 ARM 9 则执行控制功能 (如图 1 所示)。

图 1 传统的双内核 DSP/RISC 处理架构

另一种方法是在单个设备中集成 DSP 与微处理器,我们可向 RISC 内核添加类似于 DSP 的指令(如乘法或累加指令)或向 DSP 内核添加类似的控制指令(如执行特定寻址任务的指令),从而实现上述目的。凭借相关工具的支持,这种“集成化”技术具有一定的优势,如在操作系统上仅运行唯一的原生应用,这样就能简化设计方案,便于集成,并加快产品上市进程。

在传统嵌入式应用中,分别采用通用微处理器(或微控制器)和DSP内核来执行通用功能与信号处理算法。上述方法的合理性在于:

*SP 内核专门运行信号处理算法,效率较高;

*SP 架构共享一系列常见功能,如并行计算与移动、快速乘法累加 (MAC) 运算以及Harvard 架构等,支持多个运算的同时存取;

*SP处理器通常不采用RISC设计原理;

*SP架构是在电信及多媒体领域的视频、影像与语音处理等应用以及数据压缩与解压缩功能的驱动下应运而生的;

*SP 指令集以存储器为导向,并针对过滤与转换等信号处理算法的执行进行了精心优化。为了支持上述运算,DSP 采用专用寄存器、地址单元、乘法累加单元及片上存储器等。

系统应用分组的最大挑战在于,每个内核都需要自己的外部存储器子系统,这会增加功耗。除了控制独立存储器子系统所需的功耗之外,通常每个内核还要控制自己的一套外设,以实现处理内核数据的存取(如图1所示,DSP 及 ARM 与各自可能互不相同的一套外设及存储器子系统相连),这也会增加功耗,而且还会加大整体系统通信开销。

向 RISC 内核添加 DSP 指令

在 RISC 架构中集成 DSP 单元不仅能够实现更多并行操作,而且还更有效地共享资源(如外设及存储器等)。因此,采用速度更快的 RISC 架构,DSP算法的执行速度也相应地提高了。

不过,RISC 架构采用负载/存储原理,指令集的通用性较强,因此会对性能造成负面影响。有关设备的高速缓存技术比较复杂且大量使用管线处理,从而需要较高的时钟频率。基于 RISC 的微处理器添加增强型 DSP 功能与特性后,可支持乘法累加指令等 DSP 算法,也能支持图像或影像处理等专门单元。

由于带 RISC/DSP 双内核的处理器能够完成两个单核处理器的工作,因此不存在处理器间通信的问题。利用集成内核,我们可在 DSP 与控制器上动态进行代码分组,以适应系统要求或环境的变化。这种模式不仅能够加快环境转换,而且由于无需两套外设或存储器,因此进一步降低了资源占用。此外,这种方法还提高了系统的集成度,这不仅有助于降低功耗,而且还能通过在单个设备上集成更多功能而实现成本降低、性能提高及芯片尺寸缩减等其它多种优势。

如前所述,现代 DSP 处理器本身具备一些通用特性,如配置用于 DSP 运算的专用数据路径、以DSP 为中心的运算所需的专用指令集、满足多个时序存储器存取所需的多个存储体与总线,以及DSP 的专用外设等。

另一方面,通用处理器也在自身内核中集成了类似 DSP 的功能。我们可采用多种方法来为通用处理器添加 DSP 功能。设计人员可添加专用的单指令、多数据指令以及诸如多媒体扩展指令集 (MMX)指令等,也可为多个取操作数在现有 CPU内核(如瑞萨SH-DSP)上集成类似于定点 DSP 处理器的数据路径及其它相关资源。与ARM 公司的 NEON 架构类似,我们还可向 CPU 添加 DSP协处理器。设计人员也可创建三内核处理器等混合架构。

带有集成 DSP 功能与特性的架构

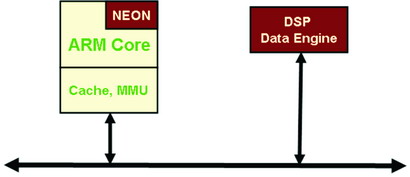

NEON SIMD 指令能并行处理 16 个元件,这加速了媒体及 DSP 应用。有关指令与内核密切配合(如图 2 所示),这种集成技术使我们能统一查看与 ARM 内核共享的存储器的情况,从而能使用统一的指令流,明确统一的平台目标,进而加速整体应用开发进程。

图 2 ARM NEON 架构

这种架构对 3G 手机等特定应用而言非常适用。就这种应用来说,DSP 数据引擎可用于视频编码等专门的处理工作,而集成了NEON DSP 功能的 ARM 内核则可用于音视频解码,RISC 处理引擎则可用于用户界面及协议栈处理等。

三内核架构(如图 3 所示)将类似于 MCU 的 RISC 负载/存储型架构与类似 DSP 的 Harvard 存储器架构结合在一起,地址总线均为 32 位宽。程序与数据存储器总线为 64 位宽。内核本身不包含任何存储器,不过可由设计人员定制。超标量架构包括 32 位定点数据通路、负载/存储单元及程序控制单元等。该设备每个循环能执行多达三个指令(数据通路指令、负载/存储指令以及指定回路的指令),这适合高性能DSP应用的需求。

图3 三内核构架

有关设备还支持各种 DSP 寻址模式,其中包括带前后增量的寄存器间接寻址、索引寻址、循环(自动模数)寻址及位翻转寻址等。位翻转技术对译出FFT算法的输入输出很有用,这是常见的DSP操作。此外还支持零开销硬件循环。

总之,采用集成 RISC/DSP 处理器支持实时嵌入式系统的优势在于:

*不影响DSP与微控制器性能的条件下,单个架构完美集成了DSP与微控制器的功能与特性;

*速任务切换功能使集成内核能像虚拟处理器一样工作,并在DSP与微控制器任务间实现快速切换,有时仅需几个时钟周期;

*大的片上存储器块(RAM 与 ROM)有助于提高系统性能并降低功耗;

*成架构无需额外的粘接逻辑便可直接控制片上外设。

评论