为多处理器系统选择最佳设计方案

过去开发一个多处理器应用,可能只需要写下那些要求,核对一下那些大型DSP供应商所供应的器件的规格,然后选择最好的芯片就可以了。但时代已经变了,今天的工程师们有了更多的选择。大型FPGA供应商改进了他们的信号处理产品,而选择最佳方案则变得复杂。

在本文中,我们将探讨一下多处理器系统有什么可以利用的,以及如何在DSP、FPGA或者二者的混合方案之间作出最好的选择。我们将分别简单地讨论这两种芯片,但将主要内容更多地集中在系统级因素上。

对于高性能信号处理应用,当然还有除DSP和FPGA之外的其它选择。ASIC和ASSP都能很好地适用于某个特定的信号处理应用,但仅限于在大规模应用中,否则它们的高成本都会让它们无法成为优选。

已获认可的DSP方案

自从20世纪80年代被发明以来,DSP一直以合理的功耗和价格提供着优越的性能。对于很多基于不断快速改变的新兴标准的应用来说,DSP都很有吸引力。由于DSP算法可以很容易地以C语言等简单语言来执行,就能在标准发生变化时更容易地对代码进行更新来反映这种变化。

另外,很多用于最新无线标准等应用领域的信号处理算法的复杂本性,使之更适合利用DSP来执行:一个DSP设备可以通过呼叫一个不同的软件程序来更容易地改变处理算法。尽管现在的FPGA可以快速重配,但要在继续处理数据的情况下动态地实现这一点,则是非常复杂且很有挑战性的。

DSP在功耗方面也在不断改进。在手持设备市场的需求驱动下,一些下一代高性能DSP结合了功耗管理技术。这可以让整个系统的功耗在低数据量时得到降低,或者用来阻止过热。一个功耗和温度敏感型FPGA配置也能以相似的方式来管理其时钟域,但需要更多的开发工作。

但是,DSP并不特别适合并行处理:有些并行处理任务可能只需要一个FPGA,却会需要多个DSP。比如,在无线基带领域,对于WiMAX直角频分多路存取(OFDMA)通道的处理来说,一个纯DSP方案在所能处理的带宽和通道数量上无法匹敌一个FPGA方案。因此DSP方案就会产生过高的成本和功耗。

灵活的FPGA方案

FPGA相比于DSP有一个很大的优势:在并行应用中的效率-这是通过采用多个并行处理区块来实现的。FPGA拥有能让嵌入式系统设计者将设备和应用实现最完美匹配的灵活性,并能以每通道较低的成本达到最高的数据吞吐量。

FPGA虽然具有很高灵活性,但相比于硬接线式架构,它的门极数量和非优化型方案的硅面积增加,因而在功耗上产生了额外的成本。但是,65纳米技术和性能相当的ASIC技术在量产中的应用,让FPGA不仅能在实验室环境中降低功耗,还能在量产中也将功耗进一步降低。

尽管芯片层的功耗更高,但FPGA的通道平均功耗可以比DSP的低很多。DSP一般功耗只有3~4W,而FPGA的功耗为7~10W,但FPGA能处理相当于DSP的十倍的通道密度。

近几年来,人们对DSP优势的推崇已经转变成为将FPGA和DSP技术结合起来,比如Xilnx Virtex-5 SXT系列产品。这让FPGA能够结合DSP算法处理,执行原本非并行的任务。这样的“基于DSP”的FPGA在某些信号处理应用中已经显示出了巨大的吞吐量优势,这一点通过其在高端处理市场的成功就得到了很好的反映。但是,FPGA一般不适合处理连续有条件型数据流。

编程FPGA仍然很难,一般需要一种偏向硬件的语言,例如Verilog或VHDL。FPGA方案的代码会比DSP方案长出数倍,这样会增加开发成本,并延长上市时间。

基于C语言的合成工具还没有实现C编码式处理器方案的易用性和高性能。高级合成工具例如Simulink区块图合成目前还没有得到广泛应用,而老的FPGA合成方法仍然延续着,尤其是当需要最大性能时。

混合多处理器系统

从一个设计工程师的角度来讲,FPGA和DSP的同步开发让他们能够找到用于信号处理应用的更新更好的方案。关于FPGA和DSP哪个更好的问题并没有一个简单的答案,而对于很多应用来说一个混合式系统才是最好的选择。这个系统结合了两种技术来提供一个方案,而这样的方案要比二者单纯相加要更好一些。

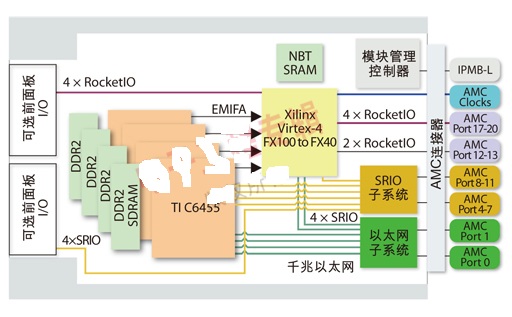

图1展示了一个标准的刀片子系统,其中包括了4颗TI公司的DSP和1颗Xilinx的FPGA。除了在DSP和FPGA之间采用EMIF连接来实现最小过空的协处理,这个子系统还带有一个全Serial RapidIO (SRIO)架构,使其能够用于无线电数据发送,并可用作卡上和卡外两个设备间的一个低延迟直接内存存取。

图1:DSP/FPGA模块(AMC-D4F1)架构图

先进夹层卡(AMC)外形的可升级性贯穿了整个基架,尤其是当系统以SRIO作为主要数据传输接口而构建的时候。在先进电信运算架构 (ATCA) 或MicroTCA基架系统中,集成者都可以选择混合并匹配以DSP为中心的刀片和以FPGA为中心的刀片,来实现恰当的技术平衡。

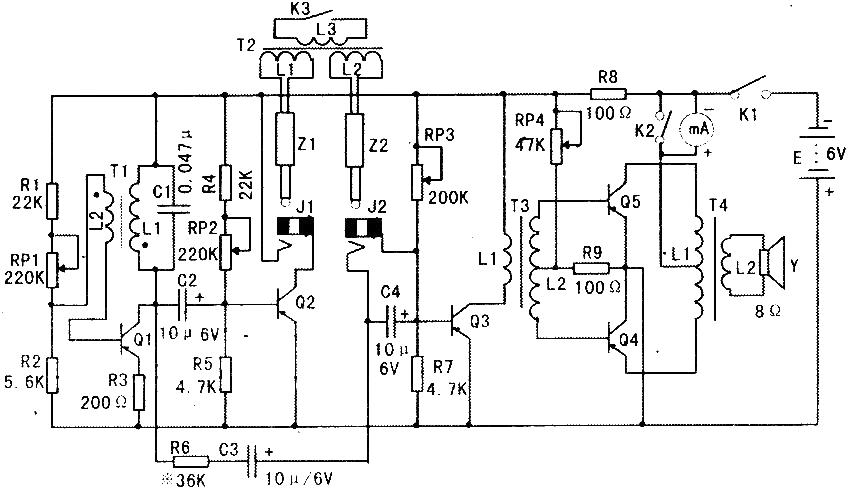

为了开发高效的混合系统,SRIP等协议以及AMC等标准让设计者和集成者可以在刀片和系统两个层面上把握平衡。图2就展示了一个典型的混合系统。

图2:采用RapidFET系统管理和分析软件的SRIO系统软件解析图.

图中可以看到终点和转接点的结合。这个系统包含了CommAgility AMC-D4F1卡等各种卡。

在CommAgility,我们的目的是通过提供一套包含了多个FPGA或DSP的AdvancedMC来确保设计者能够开放选择。这包括AMC-D4F1 (带有4个TI的TMS320C6455 DSP和1个Xilinx的Virtex-4 FX系列FPGA)和AMC-D1F3(提供了1个DSP和3个FPGA)。这让开发人员可以根据其整体处理要求、应用开发和优化阶段以及有关DSP和FPGA的现有代码库的经验,来改变所用的技术。

将SRIO用到卡上和基架中让各种元器件可以放到一起;AMC-D4F1利用了两个4倍SRIO接口,提供了两个高速的10Gbps链路,在MicroTCA,即将批准的AMC.4规格将成为系统jigsaw中的最后一个部分,尽管它并没能阻止目前已经非常流行的SRIO AMC生态系统。目前已经有多家厂商在提供SRIO支持,既支持MicroTCA网络中心运供应商,还支持控制和信号处理AMC卡。

互连的重要性

让我们回到先前那个无线基带处理的例子。如今一个一般的WiMAX基带系统可以每个基站拥有24~48个天线数据流,数据速率可以达到每个数据流123 Mbps。这样天线数据的总速率就达到了3~6 Gbps。

在以通过CDMA等扩展频谱技术编码的通道来支持多输入多输出(MIMO)系统的同时,所有基带处理区块还要获得来自所有广播天线的数据。为了实现这样的良好性能,关键是要有一个高效的低延迟互连。

相比于以太网,Serial RapidIO (SRIO)的协议过空更低,而且它和PCI Express不一样,可以支持多个主站,所以SRIO在这种多天线系统中正日益流行。此外,SRIO的多点传送功能在面向这类应用的分布式系统中也是非常重要的。

SRIO还很适合于其它高性能信号处理应用,包括雷达、成像和信号智能等。在这里,多点传送可以成为一个非常有用的功能,比如在数据需要被发送到多个DSP的IPTV服务器等视频处理应用中。

在适应外部天线时,FPGA方案会有一些困难。如今,执行一个SRIO接口所需要的逻辑元件可以达到数千个门极,这个接口相比于DSP的硬连线接口来说是很珍贵的。FPGA厂商也实现了这一点,比如Xilinx的Virtex-5就推出了一个硬核PCI-Express接口。要避免这样产生的成本,有一个很好的办法就是利用一个FPGA来作为一个DSP的协处理器,其中FPGA和DSP通过DSP的外部存储器接口总线来连接,让数据能以较低的成本或者DSP处理器过空从逻辑元件的FPGA发送出来并发回到FPGA。

一个混合式DSP/FPGA系统中的无线基带处理

为了理解对于设计人员的含义,我们可以来看看上面所讨论的一个用于WiMax的特殊方案,以及该方案如何在一个DSP/FPGA多处理器板上应用。3~6 Gbps的天线数据对于C6455这样的一个DSP来说太大了,所以天线数据的处理就需要一个ASIC或FPGA来进行。

以CommAgility的AMC-D4F1 (包含了4个C4655 DSP和1 个FPGA)为例,其中天线数据的处理就是由Xilinx FPGA完成的。AMC-D4F1的卡上FPGA和AdvancedMC结构之间的SRIO连接最适合用来将天线数据从MicroTCA基架的无线电卡上传输到作为基带处理卡的AMC-D4F1。

在另一方面,WiMAX用户数据每通道的速度大约为19Mbps,而C6455 DSP则可以轻松处理多个用户通道。AMC-D4F1上的三个DSP有一个连接到FPGA的32位125MHz的外部存储器接口,而每个DSP有一个64位接口。这样就构成了一个速度至少4 Gbps的接口,让每个DSP可以处理超过100个用户通道。

AMC-D4F1的背板SRIO连接性让系统集成者可以配置多张卡来扩大到所需的基站尺寸,并使得厂商能够采用一个随需付费方案来部署基站。这是将资本支出最小化并获得收入的一个重要因素。

评论