一、概述、特点

7135是采用CMOS工艺制作的单片4 1/2位A/D转换器,只要附加译码器,数码显示器,驱动器及电阻电容等元件,就可组成一个满量程为2V的数字电压表。

7135主要特点如下:

1 在每次A/D转换前,内部电路都自动进行调零操作。

2 在±2000字(2V满量程)范围内,保证转换精度±1字。

3 具有自动极性转换功能。

4 输出电流典型值1PA。

5 所有输出端和TTL电路相容。

6 有过量程(OR)和欠量程(UR)标志信号输出,可用作自动量程转换的控制信号。

7 输出为动态扫描BCD码。

8 对外提供六个输入,输出控制信号(R/H,BUSH,ST,POL,OR,UR),因此除用于数字电压表外,还能与异步接收 /发送器,微处理器或其它控制电路连接使用。

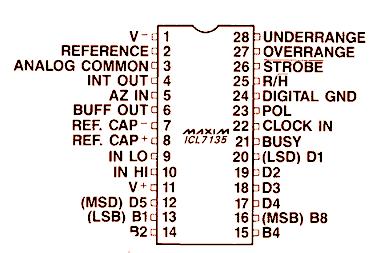

9 采用28外引线双列直插式封装,外引线功能端排列如图所示。

各外引线功能端文字符号说明如下:

V- ——负电源端,

REFERENCE —外接基准电压输入端,

ANALOG COMMON——模拟地,

INT——积分器输出,外接积分电容(Cint)端,

AZ——外接调零电容(Caz)端,

BUFF——缓冲器输出,外接积分电阻(Rint)端,

Rr+、Rr-——外接基准电压电容(Cr)端,

INLO、INHI——被测电压(低、高)输入端,

V+——正电源端,

D5、D4、D3、D2、D1——位扫描选通信号输出端,其中D5(MSD)对应万位数选通,其余依次为D4、D3、D2、D1(LSD,个位),

B8、B4、B2、B1——BCD码输出端,采用动态扫描方式输出,

BUST——指示积分器处于积分状态的标志信号输出端,

CLK——时钟信号输入端,

DGNG——数字电路接地端,

R/H——转换/保持控制信号输入端,

ST——选通信号输出端,主要用作外部寄存器存放转换结果的选通控制信号,

OR——过量程信号输出端,

UR——欠量程信号输出端。

在电路内部,CLK和R/H两个输入端上分别设置了非门和场效应管的输入电路,以保证该两端在悬空时为高电平。

V+ = +5V,V- =-5V,TA=25℃,时钟频率为120KHz时,每秒可转换3次。

功耗:1000mW(MAX);电源电压:V+:+6V(MAX);V-:-6V(MAX)

二、7135数字部分

数字部分主要由计数器、锁存器、多路开关及控制逻辑电路等组成。7135一次A/D转换周期分为四个阶段:1、自动调零(AZ);2、被测电压积分(INT);3、基准电压反积分(DE);4、积分回零(ZI)。具体内部转换过程这里不做祥解,主要介绍引脚的使用。

1、R/H(25脚)

当R/H=“1”(该端悬空时为“1”)时,7135处于连续转换状态,每40002个时钟周期完成一次A/D转换。若R/H由“1”变“0”,则 7135在完成本次A/D转换后进入保持状态,此时输出为最后一次转换结果,不受输入电压变化的影响。因此利用R/H端的功能可以使数据有保持功能。若把 R/H端用作启动功能时,只要在该端输入一个正脉冲(宽度》300NS),转换器就从AZ阶段开始进行A/D转换。注意:第一次转换周期中的AZ阶段时间为9001-10001个时钟脉冲,这是由于启动脉冲和内部计数器状态不同步造成的。

2、/ST(26脚)

每次A/D转换周期结束后,ST端都输出5个负脉冲,其输出时间对应在每个周期开始时的5个位选信号正脉冲的中间,ST负脉冲宽度等于1/2时钟周期,第一个ST负脉冲在上次转换周期结束后101个时钟周期产生。因为每个选信号(D5--D1)的正脉冲宽度为200个时钟周期(*只有AZ和DE阶段开始时的第一个D5的脉冲宽度为201个CLK周期),所以ST负脉冲之间相隔也是200个时钟周期。需要注意的是,若上一周期为保持状态(R/H=“0”)则 ST无脉冲信号输出。

ST信号主要用来控制将转换结果向外部锁存器、UARTs或微处理器进行传送。

3、BUSY(21脚)

在双积分阶段(INT+DE),BUSY为高电平,其余时为低电平。因此利用BUSY功能,可以实现A/D转换结果的远距离双线传送,其还原方法是将BUSY和CLK“与”后来计数器,再减去10001就可得到原来的转换结果。

4、OR(27脚)

当输入电压超出量程范围(20000),OR将会变高。该信号在BUSY信号结束时变高。在DE阶段开始时变低。

5、UR(28脚)

当输入电压等于或低于满量程的9%(读数为1800),则一当BUST信号结束,UR将会变高。该信号在INT阶段开始时变低。

6、POL(23脚)

该信号用来指示输入电压的极性。当输入电压为正,则POL等于“1”,反之则等于“0”。该信号DE阶段开始时变化,并维持一个A/D转换调期。

7、位驱动信号D5、D4、D3、D2、D1(12、17、18、19、20脚)

每一位驱动信号分别输出一个正脉冲信号,脉冲宽度为200个时钟周期,其中D5对应万位选通,以下依次为千、百、十、个位。在正常输入情况下,D5-- D1输出连续脉冲。当输入电压过量程时,D5--D1在AZ阶段开始时只分别输出一个脉冲,然后都处于低电平,直至DE阶段开始时才输出连续脉冲。利用这个特性,可使得显示器件在过程时产生一亮一暗的直观现象。

评论