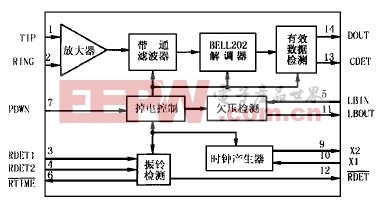

HT9030应用电路及引脚功能、管脚排列定义图

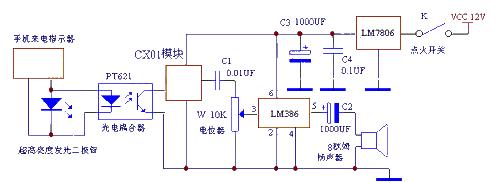

HT9030应用电路

HT9030的引脚功能、管脚排列定义图

HT9030 采用双列直插16 脚封装,引脚排列及内部结构如图3 所示。各引脚功能如下:

VDD 、VSS :分别是正电源和地;

TIP 、RIN G: 分别连接至电话线的两端。工作时, TIP 、RIN G 应与电话线引出端分别串接一0. 1μF 的电容器,以实现电话线之间的直流隔离;

RDET1 : 通过衰减网络检测振铃能量并启动振荡器和铃流检测电路;

RDET2 : 通过衰减网络将振铃信号耦合至铃流检测电路;

LBIN :低电压检测输入端;

RTIME :此端外接RC 网络,因此,此端在铃流信号的峰值间的电压低于2. 2 伏。它控制内部上电并激活局部电路以判断来电是否有效;

PDWN : 此端为高电平时, 芯片处于掉电模式;为低电平时,芯片被激活;

X1、X2 :外接3. 58MHz 晶振或陶瓷振荡器;

LBPU T :当LBIN 端的电压低于内部参考电压时,输出高电平,否则输出低电平;

RDET : 当检测到有效振铃信号时, 此端口变低。该脚与PDWN 脚相连时可自动上电;

CDET : 当检测到电话线上的有效载频时,此端口变低。芯片内置延时电路,允许载频的瞬时偏移。此脚与PDWN 脚相连可用于自动上电;

DOU T : 当CDET 脚处于低电平时, 此端输出解调信号, 数据流包括交替的1、0 和150ms 的标记信号,标记信号位于数据的前端。其它时间,端口保持高阻态。芯片内部由时钟产生电路、振铃检测电路、掉电控制电路、欠压检测电路以及BELL 202 FSK 解调电路组成。振铃检测电路的作用是检测电话线路上的振铃信号, 当检测到有效的铃流信号时, 芯片的12 脚输出低电平, 同时触发时钟产生电路和掉电控制电路, 从而使整个芯片处于工作状态。

然后, 紧随铃流的BELL 202 FSK 信号从芯片的1、2 脚输入, 经放大器、带通滤波器、解调器和有效数据检测电路, 将主叫号码信息从14 脚输出。

评论