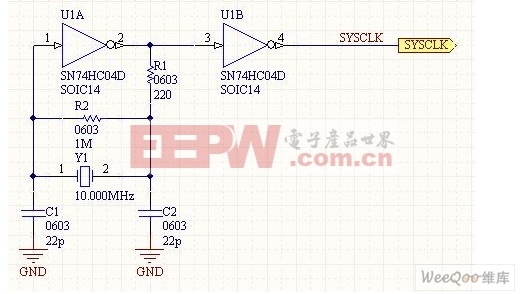

由74HC04和晶振组成的电路产生时钟信号电路图

时钟信号为CMOS电平输出,频率等于晶振的并联谐振频率。74HC04相当于一个有很大增益的放大器;R2是反馈电阻,取值一般≥1MΩ,它可以使反相器在振荡初始时处于线性工作区,不可以省略,否则有时会不能起振。R1作为驱动电位调整之用,可以防止晶振被过分驱动而工作在高次谐波频率上。C1、C2为负载电容,实际上是电容三点式电路的分压电容,接地点就是分压点。以接地点即分压点为参考点,输入和输出是反相的,但从并联谐振回路即石英晶体两端来看,形成一个正反馈以保证电路持续振荡。C1、C2会稍微影响振荡频率。

74HC04可以用74AHC04或其它CMOS电平输入的反相器代替,不过不能用TTL电平输入的反相器,因为它的输入阻抗不够大,远小于电路的反馈阻抗。

实际使用时要处理好R1和R2的值,经试验,太小的R1或太大的R2会有可能导致电路工作在晶振的高次谐振频率上(常见的是3次谐波,10MHz的晶振会产生30MHz的频率输出)。对于10MHz的晶振,采用R1=220Ω、R2=1MΩ可以使电路稳定输出10MHz的方波时钟信号。

评论