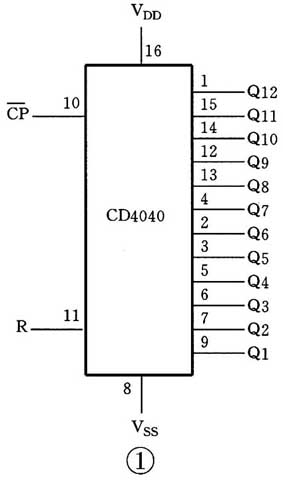

这次无线电小组的活动内容,是用中规模集成电路12位二进制串行计数器/分频器CD4040(图1)组装“电子音叉”电路,然后由老师指导大家学习了二进位计数制和二进制计数器的工作原理,并一起分析了应用电路。

同学:老师,请问您,在数字电路中为什么一定要采用二进制计数呢?二进制的计数规则是什么?

老师:人们都习惯于使用十进制计数,十进制数有10个数码,要使计数电路具有10种不同的状态,分别表示0、1、2、3、4、5、6、7、8、9这10个数码,几乎是不可能的。大家知道,门电路和触发器很容易获得两种不同的状态,可以分别用来表示0和1两个数码,用它们组成计数电路简单、方便。因此,在数字电路中普遍采用二进位计数制,简称二进制。二进制的计数规则是逢二进一,不管数值大小都只由0和1两个数码组成,每个数码在二进制数中所处的位置不同而有不同的含意。例如,有一个二进制数为“110101”,按照从低位到高位逢二进一的规则,最右边第一位数是2

0位,第二位数是2

1位,第三位数是2

2位,依次向左,分别是2

3位、2

4位和2

5位。这样,二进制数“110101”化成十进制数的数字表示式可以写成(110101)

2=(1×2

5+1×2

4+0×2

3+1×2

2+0×2

1+1×2

0)

10=(32+16+4+1)

10=(53)

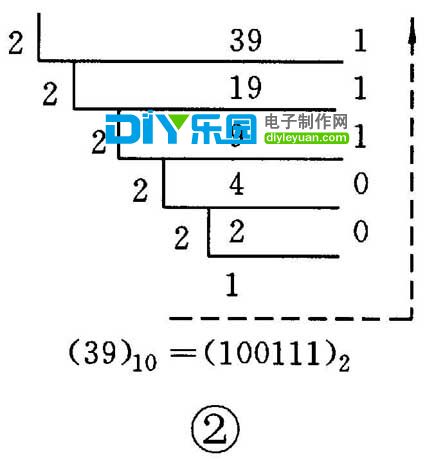

10同学:怎么把一个十进制数化成二进制数呢?

老师:要把一个十进制数转换成二进制数,只需要把这个数除以2,除得尽时,最低位数就是0;除不尽,最低位数就是1。再把它的商除以2,除得尽,则末前位(2

1位)为0;除不尽,末前位数为1。再把它的商除以2……,直到所得商为1为止。例如,十进制数“39”转换成二进制数,可以按上面说的方法列出图2所示的算式。图中箭头表示由高位到低位的方向。由图可以算出(39)

10=(100111)

2。

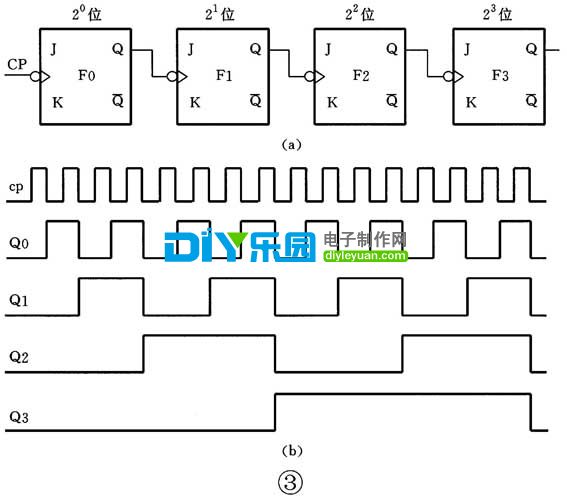

同学:我们对触发器的印象是很深的。在JK触发器的逻辑功能中有“J1K1,分频计数”。是不是用JK触发器就可以组成二进制计数器呢?

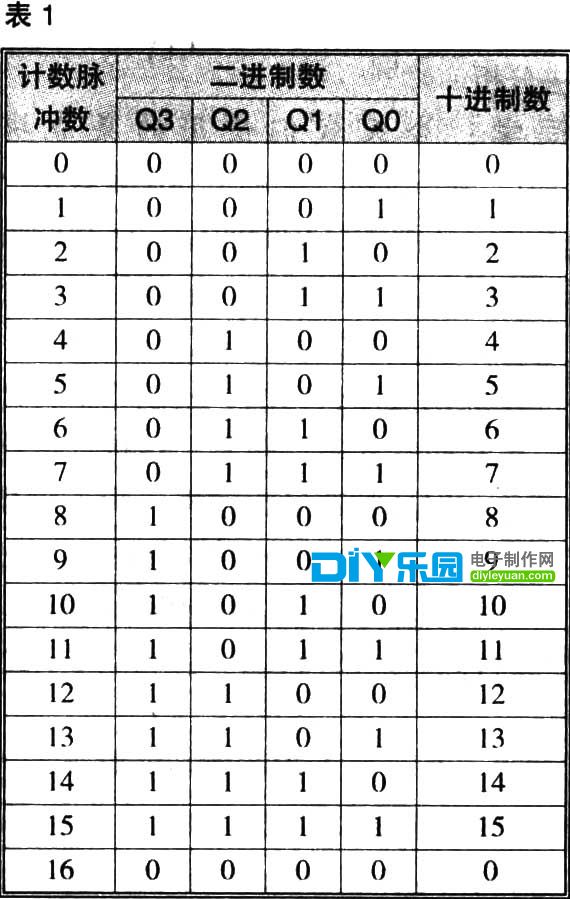

老师:对。一个触发器可以作为二进制计数器的一个计数值。我们先来分析一个四位二进制计数器的逻辑图和波形图(图3)。假设在计数开始前,各位触发器都置0。当第1个时钟脉冲CP的下降沿到来时,触发器F0翻转,Q0由0变1。由于各位触发器都是用下降沿触发的,所以Q0发生从0到1的正跳变时,F1不会翻转,当然F2、F3的状态也不会改变,计数器的状态是“0001”。第2个CP脉冲到来时,F0又翻转一次,Q0由1变0,触发F1,使Q1由0变1,F2、F3的状态仍然不变,计数器的状态是“0010”。第3个CP脉冲到来时,F0又翻转,Q0又由0变1,所以F1、F2、F3的状态不变,计数器的状态变为“0011”。如此继续下去,一直到第15个CP脉冲过后,触发器的状态成为“1111”。如果再来第16个CP脉冲,计数器将变为“0000”,并向高位送出进位脉冲。从波形图〔图3(b)〕可以直观地看出,从Q0→Q1→Q2→Q3,都是逢二进一,实现了二进制加法计数的功能。计数器中各位触发器输出波形的组合,称为时序图。为了分析方便,常常把时钟脉冲顺序输入时,对应的计数器状态列成表(表1),称为状态转换表。

同学:有的触发器是采用上升沿触发的,我在画这类计数器的时序图时,发现计数器的状态完全不对,这是怎么回事呢?

老师:你提的问题很好。如果触发器是采用上升沿触发,就必须把前一级的端接到后一级的CP端,才能进行加法计数。否则,就变成减法计数了,大家可以自己去分析。

同学:今天我们使用的集成块CD4040,为什么叫二进制串行计数器呢?

老师:从刚才分析的四位二进制计数器的逻辑图(图3)可以看出,进位信号是逐级传送的,也就是数字信号是按F0→F1→F2→F3串联的顺序进行的,所以叫串行计数器,也常叫它异步计数器。这种计数器结构简单,但计数速度比较慢。为了提高速度,人们设计出一种把时钟脉冲CP同时加到各位触发器上,使各位触发器的状态转换与时钟同步的计数器,称为同步计数器。

同学:您能给我们介绍一下同步二进制计数器的结构和工作原理吗?

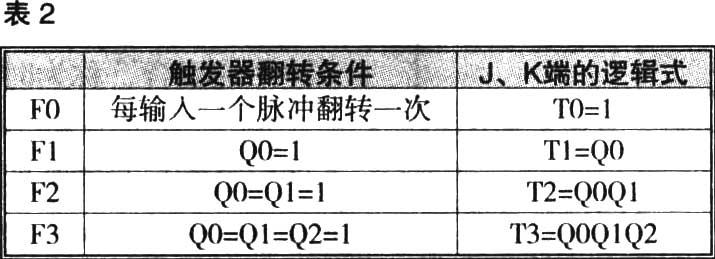

老师:同步二进制计数器并不复杂,根据同学们学过的知识,完全可以设计出它的逻辑电路。大家知道,JK触发器的计数功能是“J0K0,输出不变;J1K1,分频计数”。所以,需要把各触发器的J、K端连在一起,作为控制端T。T端与前一位触发器的Q端通过什么方式连接呢?请大家再来分析计数器的状态转换表(表1)。根据状态转换表,哪位同学说说各位触发器的翻转条件?

同学:从状态转换表上可以看出,F0是每来一个时钟脉冲翻转一次(T0=1);F1是在Q0=1时,时钟脉冲到来才能翻转(T1=Q1);F2是在Q0=Q1=1时,时钟脉冲到来发生翻转(T2=Q0Q1);F4是在Q0=Q1=Q2=1时,时钟脉冲到来才会翻转(T3=Q0Q1Q2)。

老师:说得不错。把你的分析结果列成表(表2),就能看出同步二进制计数器的控制条件了。现在请一位同学画出同步二进制计数器的逻辑电路。

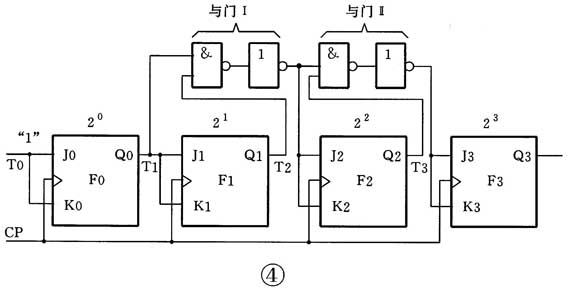

同学:我来试试看。先画出四位触发器(图4),把输入时钟脉冲直接接到各位触发器的CP端。按照表2中所列J、K端的逻辑式,T0固定接高电平1;T1接在Q0端;将Q0与Q1经过与门I接在T2端;再将与门I的输出Q0Q1和Q2经过与门Ⅱ接在T3端。这样,就可以实现各位触发器状态的转换与时钟脉冲同步了。

老师:完全正确。大家只要熟练地掌握了门电路和触发器的逻辑功能,就可以灵活地设计简单的时序逻辑电路了。

同学:您在介绍“电子音叉”电路(图5)时曾说过,CD4040是作为分频器使用的,那么计数和分频到底有什么不同呢?

| 1 | | 1 | |

| 老师:概括地说,二进制计数器的计数过程同时也是分频过程。请看时序图〔图3(b)〕,以输入时钟脉冲CP的频率fcp为主频率,触发器F0对主频率进行了二分频,就是fQ0= | -- | fcp,分频系数是2;F1对主频率进行了四分频,就是fQ1= | -- | fcp, |

| 21 | | 22 | |

| 1 | | 1 | |

| 分频系数是4;依次是fQ2= | -- | fcp、fQ3= | -- | fcp,分频系数分别是8和16。CD4040是12位二进制计数器,大家可以算出,它的最大分频系数为212=4096。 |

| 23 | | 24 | |

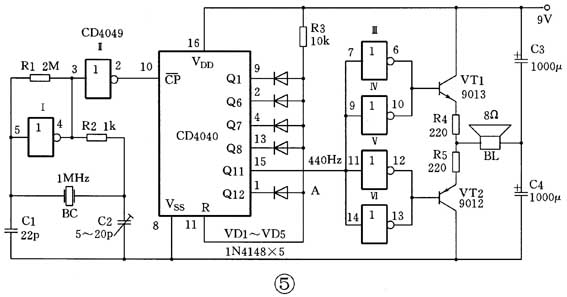

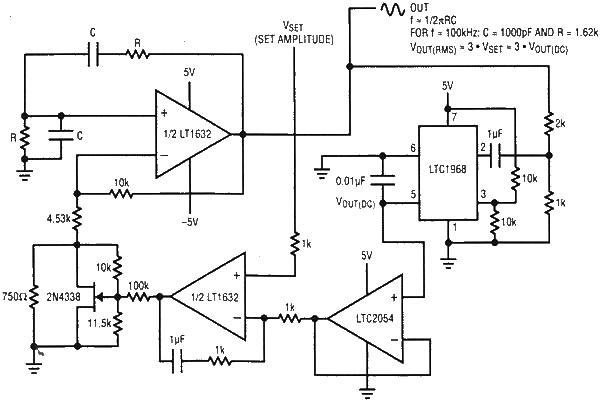

同学:明白了。按照您教给我们的“化整为零”的识图方法,我说说“电子音叉”电路的组成和工作原理,不对的地方请您指正。在电路中,非门I及石英晶体BC组成了频率为1MHz的振荡器,经过非门Ⅱ作为CD4040的时钟脉冲CP

——。CD4040将1MHz输入信号分频后,输出440Hz的音频信号,再经过非门Ⅲ~Ⅵ送到由VT1、VT2组成的互补推挽电路放大后,推动扬声器发出440Hz的国际标准A音。

老师:你的分析基本正确。需要补充说明的是非门Ⅱ是用来整形的,非门Ⅲ~Ⅵ则是缓冲电路。

同学:我计算了一下CD4040接成的分频器,分频系数是2273。但是从电路图上看不明白CD4040是怎么进行分频的,希望您再给我们讲讲。

老师:好。由于2273不是2的整数次方,不能从Q1~Q12中的某一个管脚直接获得这一分频系数,怎么办呢?首先把2273化成二进制数,也就是(2273)

10=(100011100001)

2,其中数值为1的分别为2

11位、2

7位、2

6位、、2

5位和2

0位,它们在CD4040中所对应的管脚分别为Q12、Q8、Q7、Q6及Q1,分频系数为2

0+2

5+2

6+2

7+2

11=2273。然后,通过由VD1~VD5组成的二极管与门把Q12、Q8、Q7、Q6、Q1反馈到CD4040的置0端R。当与门各输入端都是高电平1时,R端才是高电平1,从而使Q1~Q12全部置0。也就是说,在CD4040的CP端,每输入2273个脉冲,在Q11端输出一个脉冲;输入脉冲频率为1MHz,输出脉冲频率即为440Hz。

评论