如何消除高速ADC电源设计中的噪声

当今许多应用要求高速采样模数转换器(ADC)具有12位或以上的分辨率,以便用户能够进行更精确的系统测量。然而,更高分辨率也意味着系统对噪声更加敏 感。系统分辨率每提高一位,例如从12位提高到13位,系统对噪声的敏感度就会提高一倍。因此,对于ADC设计,设计人员必须考虑一个常常被遗忘的噪声源 ——系统电源。ADC是敏感器件,为了实现数据手册所述的最佳额定性能,应当同等看待模拟、时钟和电源等所有输入端。噪声来源众多,形式多样,噪声辐射会 影响性能。

当今电子业界的时髦概念是新设计在降低成本的同时还要“绿色环保”。具体到便携式应用,它要求降低功耗、简化热管理、最大化电源效率并延长电池使用 时间。然而,大多数ADC的数据手册建议使用线性电源,因为其噪声低于开关电源。这在某些情况下可能确实如此,但新的技术进步已经证明,开关电源也可以用 于通信和医疗应用1。

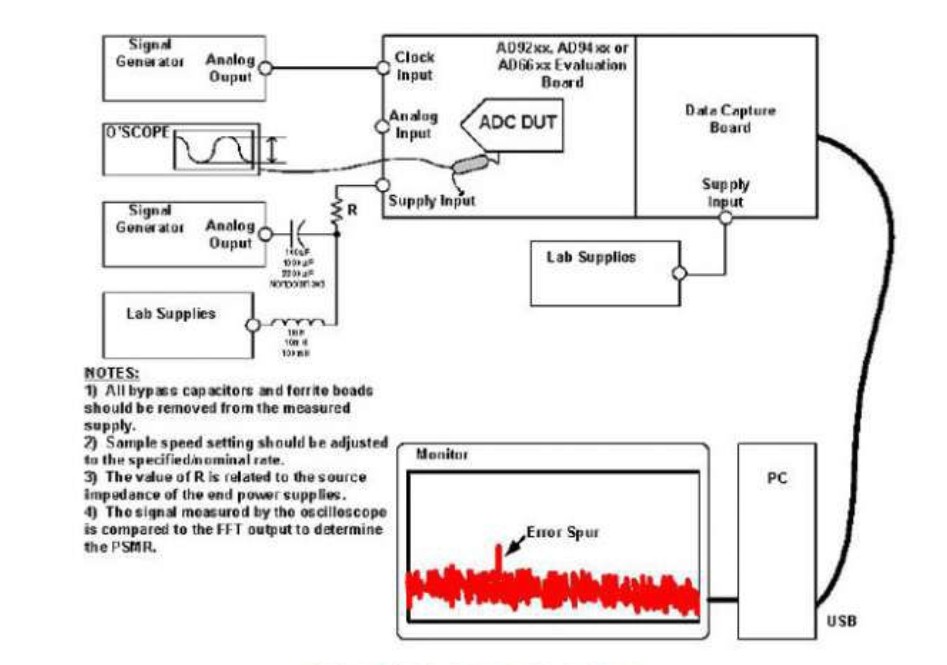

本文介绍对于了解高速ADC电源设计至关重要的各种测试测量方法。为了确定转换器对供电轨噪声影响的敏感度,以及确定供电轨必须处于何种噪声水平才能使ADC实现预期性能,有两种测试十分有用:一般称为电源抑制比(PSRR)和电源调制比(PSMR)。

评论