低成本3V电压驱动5V系统方法介绍

该文章描述了如何使用3V电压驱动5V系统。

在一个5V电压系统中使用一个3V电压器件,以下几点必须考虑:

1、一个3V供电电源必须被提供

2、5V器件驱动3V输入

3、3V器件驱动5V输入

电源供电

有几方面的因素决定如何从一个已经存在的5V电源提供一个3V供电电源,考虑5V电源的供电稳定性,考虑供电类型(例如,电池或交流整流)。另外,调节5V电源到3V将增加设计的器件数量和消耗额外的功耗,特别是在低功耗的电池应用中。

调节线性电源

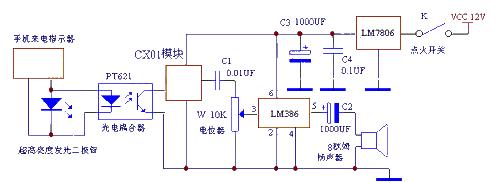

电源供电可能来自商业供电,这个供电电源是很不干净的,提供一个干净和稳定的3V电源,我们可使用LDO。

LDO必须能提供符合规格的负载电流给器件及所以在应用系统中的3V外设,这些规格参数可通过规格书查找到,例如,Silicon Labs的C8051F001在20MHz并且模拟外设有效的情况下,其电流为12mA(10mA为CPU数字供电电流,2mA为模拟外设供电电流),另外,如果其它外设如LED被使用,则需累加这些电流。

电池供电

电池一般都可提供干净的电源,但是,电池应用必须考虑低功耗,因此,DC-DC转换器将被使用到,因为相比LDO这更加高效节能。

Silicon Labs 5V兼容输入

5V直接驱动3V输入,由于超过ESD保护器件的电流,将造成器件损坏或寿命减少,但Silicon Labs的C8051FXXX系列器件可容忍5V输入,因此,设计时,可直接连接5V电压到数字输入引脚不会造成器件损坏。

用3V驱动5V输入

尽管C8051FXXX的数字输入可以容忍5V输入,但输出最高只能驱动VDD(2.7-3.6V),如果5V器件需要的输入驱动电压高于VDD,则需要额外的配置。驱动5V输入两个主要的方法为使用逻辑门和上拉电阻。

使用逻辑门接口

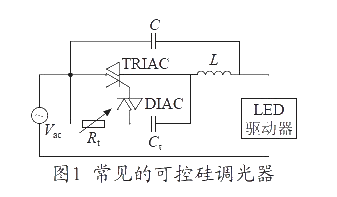

74VHCTXX系列逻辑门可用于3V驱动5V的系统接口,图1显示了如何使用74VHCTXX器件用于3V信号驱动5V信号。逻辑门接口推荐应用于高速信号,使用74VHCTXX器件其最主要的弊端是成本和板子空间。

图1 逻辑门接口

使用上拉电阻接口

相比逻辑门接口使用上拉电阻接口需要的成本更低,空间更小,上拉电阻可以用于高于VDD的应用。

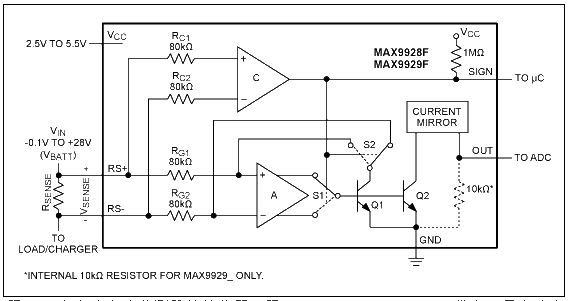

要完成这个应用,需设置输出端口引脚模式为开漏,在开漏模式,逻辑1驱动端口为高阻态,逻辑0驱动为低电平,图2显示了通过一个上拉电阻连接5V系统应用,逻辑1驱动C8051FXXX的端口到5V,逻辑0驱动到地。

图2 C8051FXXX器件驱动5V器件输入

选择上拉电阻

当端口引脚为逻辑0时,输出电压接近为0,在这种情况下,电流将通过上拉电阻和端口流到地,为了减小功耗,设计更大的电阻减小电流。

当端口引脚为逻辑1时,输出驱动端口被关闭,端口电压被拉到高电平通过上拉电阻,信号的上升沿可能很长,这由上拉电阻值和输入端的等效电容决定,在图2中,电容C通过上拉电阻的5V被充电,充电时间常数等效于如下公式:

如按键或片选信号应用中,对这个时间可以不敏感,但在如串口通讯、时钟信号同步的应用中,这个时间就很重要了,此时这个充电时间必须考虑,这将限制上拉电阻的大小,上拉电阻太大将导致过长的充电时间,从而导致端口识别逻辑1的时间加长,如图3所示,T为充电到5V器件能识别的逻辑1电压所花的时间(参考VIH),这个电压与应用和电容C的值相关,如果这个时间常数过大,可能导致5V器件在给定的方波频率内无法识别到正确的逻辑1,因此,选择上拉电阻R必须足够小,以适合输入,但又的注意太小阻值将导致过多的功耗浪费在上拉电阻上。

图3 方波充电时间图

一旦最大的可接受的上升时间T被决定了,则上拉电阻R可通过如下公式计算:

其中,Vih=逻辑1的电压,T=识别逻辑1最大可接受的时间。

在输出电压从逻辑1转换到逻辑0时,也有一个小延时,但相比上升时间,这个时间可忽略不计,从图3中可观察到,即使在C8051FXXX的端口驱动为逻辑0时,在C电容上也会有小电压存在。

如前面所述,如果电阻太小,大部分的功耗将消耗在逻辑0的状态,另外,如果电阻值过小,低电平的电压值可能过高,而不能识别到逻辑0,例如C8051F0XXX的器件是0.6V在8.5mA时,一个小的电阻可能导致更高的电流和更高的电压值对于5V输入器件。

总之,对于上拉电阻:

1、考虑足够大的值阻值电流和功耗消耗在逻辑0。

2、保证足够低的低电平值对于5V器件的逻辑0识别。

3、保证足够小的上升时间对于给定的应用。

例子

接下来的例子说明了如何计算适当的上拉电阻R在一个给定的电容C,以及逻辑电平1(Vih)的值和频率决定最大允许的上升时间T。另外需考虑在逻辑0状态下在上拉电阻上消耗的功率,最终决定上拉电阻的值。

在这个应用例子中,我们考虑C8051FXXX作为SMBus主模式(提供SCL信号到从设备)提供开漏同步时钟信号(SCL),这个信号将输出到5V电压设备,在图2中配置需保证适当的电压供电,端口引脚需配置为开漏驱动,C8051FXXX上电复位后默认为开漏配置。

一个适当的上拉电阻需考虑:

1、在逻辑0状态下最小的电流消耗。

2、对于配置的电容C和上拉电阻,上升时间不能超出性能规格要求。

3、在逻辑0状态下,端口输出的电平不能超出范围。

一个高电阻将被使用来减小功耗,尤其是在低功耗应用中(例如在电池供电的应用中)。在保证满足电压上升时间的情况下,我们计算最大电阻值,在这个例子中,电压需足够高,保证在CMOS的5V设备5% 的时钟周期内可识别到逻辑1,我们假设Vih为0.8*VDD(4V),选择SCL频率为400kHz,我们的电压需在125ns内上升到4V。

因此,参考公式2,T=125ns,Vih=4V,假设电容C=10pF(只有一个从设备连接到SCL总线上),根据公式2,我们计算R=7.77kΩ。这是该规格SCL频率和CMOS输入逻辑下的最低电阻值,一般SCL频率越低,可用的电阻值更高。

在该设计的最大电阻值情况下,我们计算在逻辑电平0状态下通过电阻的电流值,最坏情况下,我们计算电流在5V供电,通过7.77 kΩ电阻的电流为644uA,功耗大约3.2mW。

相关文档下载:相关文档下载:

Silicon Labs 单片机、无线传输芯片、广播电视芯片、隔离传感以太网供电芯片、时钟及晶振选型指南

评论