12路输出时钟发生器在无线基站上的应用

Si5380是一个高性能的时钟发生器,可以合成多达12路频率输出,输出时钟可以运行在自由模式或同步到4个外部输入之一的时钟。该时钟发生器采用Silicon Labs第四代DSPLL创新技术,具有双环路混合信号架构,消除了外部VCXO和环路滤波器的需要。Si5380时钟IC提供了媲美传统分立解决方案的相位噪声性能,特别适用于无线基础设施应用。

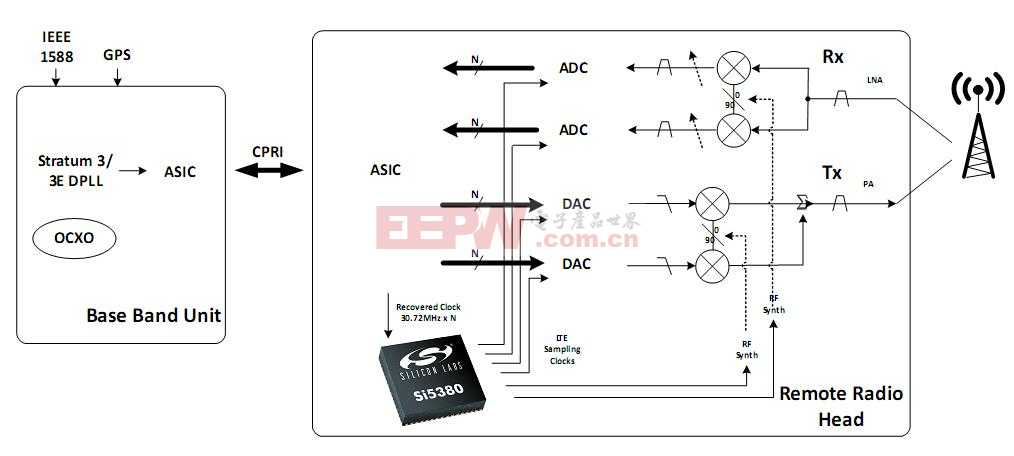

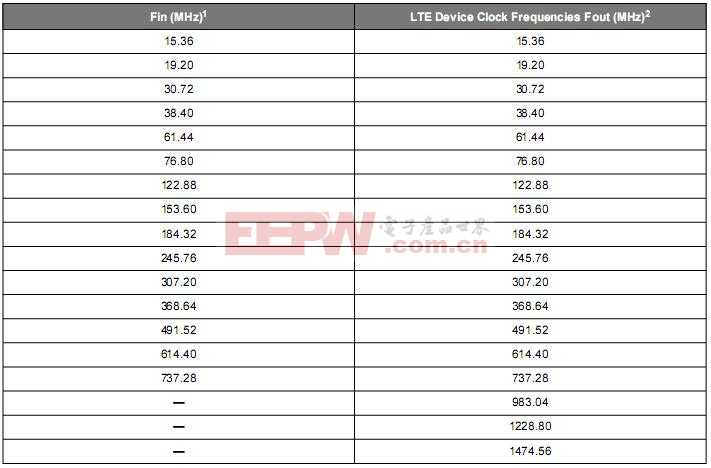

图1为Si5380在LTE无线基站RRH的典型应用框图,表一为LTE常用的采样时钟频率,Si5380的DSPLL内核能产生多达5个独立的频率,这些频率通过内部的交叉开关被分配到R输出分频,R分频可进一步分频出多达10路独立的整数倍关系时钟频率,通过Si5380可以锁定表一中任一一个输入频率,产生LTE设备需要的时钟频率。

图1: LTE无线基站RRH应用框图

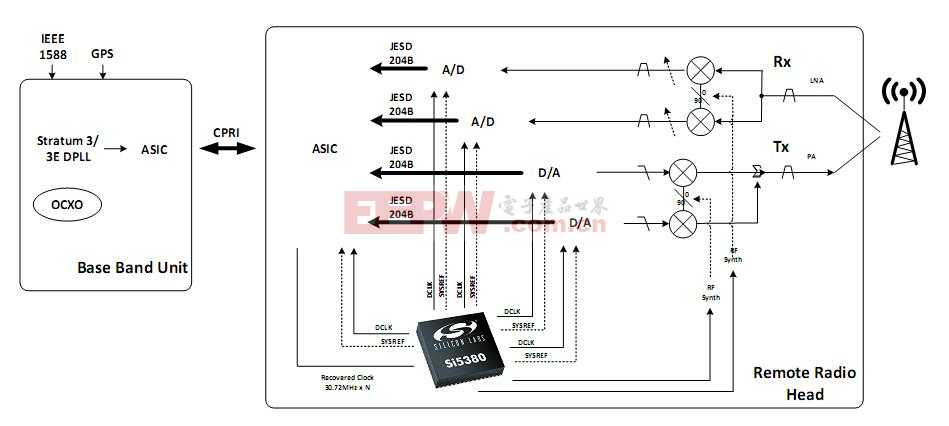

图2:LTE无线基站应用JESD204B数据转换框图

图2为Si5380在LTE无线基站应用JESD204B数据转换框图,Si5380支持JESD204B子类0和子类1时钟,12个输出时钟可独立的配置为设备时钟或系统参考时钟,可为4个JESD204B设备提供4个或更多的设备时钟和4个系统参考时钟,如果系统时钟被外部逻辑提供,则Si5380可为12个JESD204B设备提供时钟。

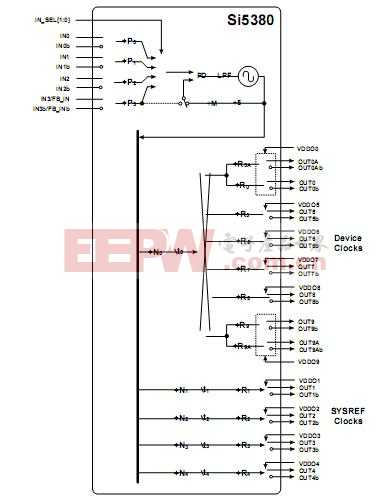

图3为产生JESD204B子类1时钟的分频例子,在这个例子中,N分频决定了设置时钟频率,R分频提供了参考时钟频率,参考时钟使用了更低的帧频率。N分频通道包含了一个延时可配置的路径,在这个例子中,所有的设备时钟共用一个可配置延时(t0),而每个参考时钟都有一个独立的延时(t1-t4),延时是68ps步进可编程的,一共128步(8.6ns)的可调。

图3:分频配置JESD204B子类1时钟举例

基于VCXO的时钟解决方案在震动环境下通常导致杂散性能衰减,而Si5380芯片集成的DSPLL技术无论在任何系统环境下都能够提供优异的杂散响应。此外,Si5380时钟芯片在锁定到高抖动输入时钟后能够保证低相位噪声,确保数据转换器性能不会受到外部影响而衰减。Si5380能够生成高达1.47456GHz的4G/LTE频率,并提供12路独立的可配置时钟输出,为兼容JESD204B标准的数据转换器、FPGA和其他逻辑器件提供定时服务。Si5380时钟是目前业界最高集成度的定时解决方案,它满足微蜂窝和宏蜂窝基站在各类环境条件下对于紧凑型PCB封装、低功耗、可靠性和运营商级别相位噪声性能的需求,是无线基站时钟应用的理想选择。世强已代理该产品多年,能保证良好的供货以及成熟的技术服务。

参考附表1: LTE常用采样时钟频率

评论