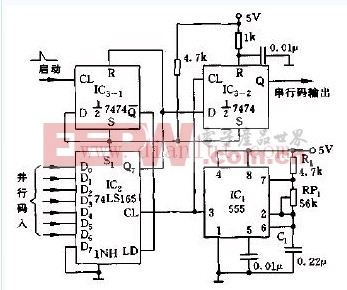

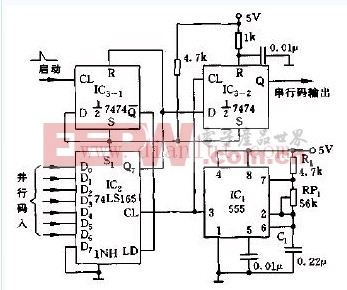

七位并行串行码转换电路原理

如图所示,IC(555)和R:、RPl、C1组成无租态多谐振荡器,产生f=1.44/(R1十RPl)Cl的脉冲,作为时钟加至IC2和IC3-2的CL端。IC3是双D触发器74LS74,加进的启动脉冲使IC3-1的Q变为低电平,使IC2移位寄存器的LD也为低电平,将并行码D.~D6寄存在其内的寄存器Q.~Q6.随着IC1的移人时钟,将寄存的码依次移人Q7,并移出IC3-2的输出端Q。

如图所示,IC(555)和R:、RPl、C1组成无租态多谐振荡器,产生f=1.44/(R1十RPl)Cl的脉冲,作为时钟加至IC2和IC3-2的CL端。IC3是双D触发器74LS74,加进的启动脉冲使IC3-1的Q变为低电平,使IC2移位寄存器的LD也为低电平,将并行码D.~D6寄存在其内的寄存器Q.~Q6.随着IC1的移人时钟,将寄存的码依次移人Q7,并移出IC3-2的输出端Q。

评论