1:LVDS器件简介

对于高速电路,尤其是高速数据总线,常用的器件一般有:ECL、BTL、GTL和GTL+等。这些器件的工艺成熟,应用也较为广泛,但都存在一个共同的弱点,即功耗大,此外,采用单端信号的BTL和GTL器件,电磁辐射也较强。现在,NS公司率先推出的CMOS工艺的低电压差分信号器件(即Low Voltage Differencial Signal 简称LVDS )给了我们另一种选择。

LVDS器件是近年来National Semiconductor公司发展的一种高速传输芯片,它的传输机制是把TTL逻辑电平转换成低电压差分信号,以便于高速传输。与传统的ECL逻辑相比,它采用CMOS工艺,它的电压摆幅更低,只有400mv,ECL为800mv,动态功耗更小,(输出电流3-5mA)只有ECL电路的1/7(相同的数据传输量),低EMI,价格更低,因而具有很大的优势,从97-98年首先在欧洲开始得到应用。目前,NS公司的LVDS器件有以下几个系列:

- Channel Link,如:DS90CR285/6,DS90CR217/218

- Bus LVDS,如:DS92LV1021/1201

- Flat Panel Display (FPD)- link,如:DS90CF385/386

- Line Drive and Receiver (LD&Rs),如:DS90LV031A/032A

LVDS器件的推出时间不长,目前,已经在欧美地区开始应用,据了解,国内目前尚没有应用,但已有几家公司在进行测试和试用。现有的LVDS器件单对差分线所能传输的最大速率为400-600M左右,据悉NS公司正在开发速率为1G的芯片组。其它公司,如TI、朗讯,都有各自的LVDS类型的芯片。3M公司则开发了LVDS信号专用的双绞电缆和接插件。LVDS器件主要用途为:电缆或PCB传输(点对点)、总线传输(BLVDS)、平板显示器(FPD)等,传输速率在400M-600M,今后的LVDS器件的速度将会提高到1G,速度越来越快,品种也会越来越多。

据目前掌握的资料,未来几年,NS将推出单对差分线传输速率达千兆位的LVDS收发器、低延迟的LVDS时钟信号缓冲器/驱动器,以及36X36LVDS信号的SWITCH芯片。另外,Ericsson 和Sony 公司已经推出传输速率超过1G的GLVDS器件。

2:LVDS器件的标准

2.1:ANSI/TIA/EIA-644

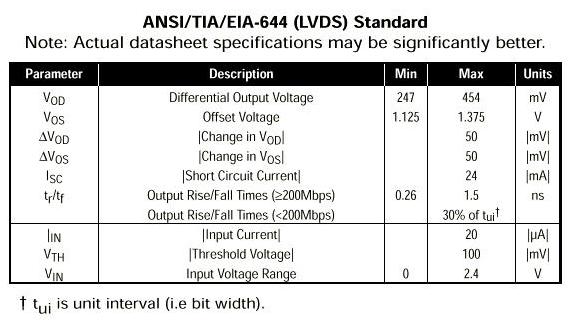

ANSI/TIA/EIA-644是由TR30.2制定的,这个标准定义了收发器的输入输出阻抗,但是这仅仅是一个电气特性标准。其并不包括功能性和协议规格,完全是应用独立的。ANSI/TIA/EIA-644打算通过使用别的协议来完善 整个接口功能。这使的这个标准在很多方面便于实现。在标准中推荐的最大操作速率是655Mbps,理论最大使用速率是1.923Gbps。传输速率与使用的介质损耗有关。这个标准同时也说明了最低的介质要求、收端的fail-safe电路、多路操作等。标准见下表:

表1:ANSI/TIA的LVDS标准

2.2:IEEE 1596.3 SCI-LVDS

SCI-LVDS被定义作为SCI的一个子集,在IEEE 1596.3中有详细说明。SCI-LVDS说明了应用于高速/低功耗物理接口的电气规范,同时也定义了用于SCI数据传输的包交换的编码格式。SCI-LVDS在特定的条件下也支持高速的RAMLINK传输。SCI-LVDS同TIA除了在一些电气要求和负载条件有差别,在别的方面十分相似。两个标准支持相似的驱动输出电平,接收门限电平,数据传输速率。在两个标准中TIA的应用更为普遍,同时TIA也支持多负载情况。

3:LVDS器件的工作原理

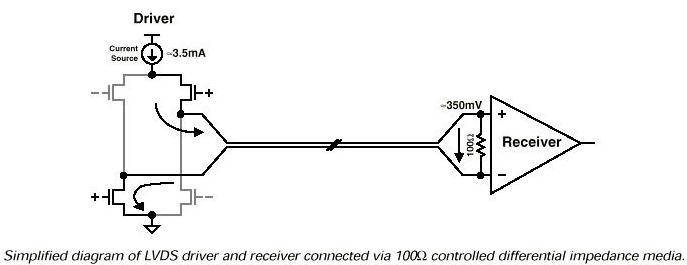

LVDS器件的工作原理如下图所示:

其中发送端是一个约为3.5mA的电流源,产生的3.5mA的电流通过差分线的其中一路到接收端。接收端对于直流表现为高阻,电流通过接收端的100欧姆的匹配电阻产生350mA的电压,同时电流经过差分线的另一条流回发送端。当发送端进行状态变化是它通过改变流经电阻的电流的方向产生有效的’0’和’1’态。

4:LVDS的特点

LVDS的特点是电流驱动模式,低电压摆幅350mV可以提供更高的信号传输速率,使用差分传输的方式可以使信号的噪声和EMI都减少:

A、低的输出电压摆幅(350mV)

B、低的信号边缘变化率, dV/dt 0.350V/0.5ns = 0.7V/ns

C、差分特征是磁干扰相互抵销。

D、软的输出切换

E、最小的Icc切换电流变化。

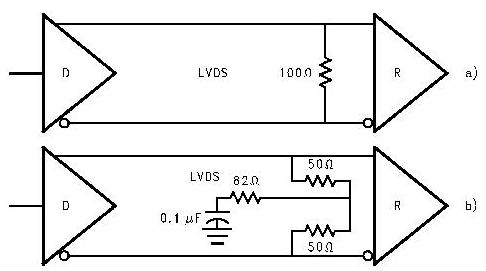

同时由于使用电流驱动模式,对LVDS电路的匹配方式极为简单,可以有以下两种方式

图3:LVDS接口信号的匹配图

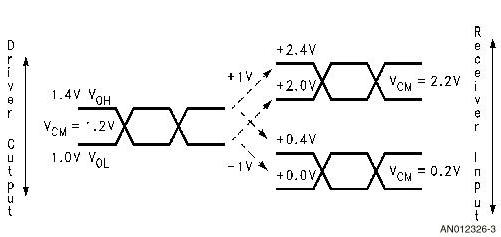

其中第一种方式最为简单,也最为实用。对第二种匹配方式对共模干扰有更好的抑制作用,但是因为差分信号本身的特点一般是没有必要的,这种匹配方式对PCB设计是的布线的难度加大,这对于高密度的PCB板的设计是不利的。对于LVDS的接收端一般可以忍受大范围的共模对地偏压。一般LVDS收端可以忍受+/-1V的在发端地和收端地之间的地漂移。LVDS的典型的驱动偏置是1.2V,加上可以承受的地漂移收端的偏置可以从0.2V到2.2V。推荐的收端输入电压范围是从地到2.4V。参见下图:

图4:LVDS的逻辑电平图

5:LVDS的设计

5.1:LVDS在PCB上的应用

LVDS在PCB的应用应该注意遵循以下准则:

- 对LVDS的使用,不论信号的数量多少,都建议使用多层板,最少四层设置,LVDS、GROUND、POWER、TTL。

- 对LVDS信号和其它信号比如TTL信号,最好能使用不同的走线层,如果因为设计限制必须使用同一层走线,LVDS和TTL的距离应该足够远,至少应该大于3~5倍差分线间距。

- 保证收发器到接插件的距离足够短,防止由于STUB线过长引起信号的崎变,一般要求距离小于10mm。

- 对收发器的电压和地使用滤波电容,滤波电容的位置应该尽量靠近电源和地管脚,滤波电容的值可以参照器件手册。

评论