USB(Universal Serial Bus)是一种通用串行总线,主要用于PC与外围USB设备的互联。近年来,USB接口以其快速、即插即用、使用安装方便等优点逐渐成为现代数据传输的发展趋势。目前,国内外采用USB1.1和USB2.0两种规范。USB1.1主要用于低速传输要求的场合,支持1.5Mb/s和12Mb/s两种传输速率;而USB2.0规范则提供高达480Mb/s的传输速率。尽管如此,在某些对数据传输速度要求很高的系统中,外围设备与USB接口之间在速度上仍存在着不可忽视的传输瓶颈。

Cypress公司生产的USB2.0控制器CY7C68013提供了一种独特的接口方式,即通用可编程接口(GPIF)方式。它与传统接口方式的主要区别有两点:

①在数据传输过程中不需要CPU干涉,使得传输速率明显提高,从而可以充分利用USB2.0的传输带宽;

②由软件设置读/写控制,其控制方式类似于状态机,提高了传输稳定性。

因此,本文介绍的基于USB2.0控制器CY7C68013的GPIF接口设计,就是充分利用了该芯片这一独特的数据传输接口方式,有效地解决了在传统接口方式下USB2.0设备数据传输速度的局限性,大大提高了数据的传输速率。1 CY7C68013简介

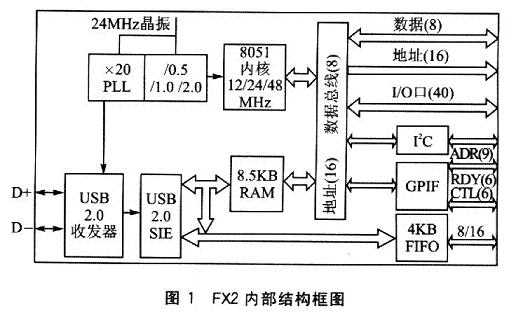

CY7C68013是Cypress公司的EZ-USB FX2系列芯片。EZ-USB FX2是一款集成USB2.0收发器的微控制器,内部结构如图1所示。该系列芯片集成了USB2.0收发器、串行接口引擎(SIE)、带8.5KB片上RAM的增强型高速8051单片机、4KB FIFO存储器以及通用可编程接口等模块.提供了全面集成的USB解决方案,无需外加芯片即可实现高速USB传输。FX2系列芯片最主要的特点是可以通过USB2.0的通用可编程接口为特定的应用接口编程。另外,CY7C68013的GPIF引擎具有自动传输数据结构的特性,这种特性使得以主/从端点FIFO(8/16位数据总线)为ATA、UTOPIA、EPP、PCMCIA、DSP等的外围设备,可以与主机通过CY7C68013无缝、高速地传输数据。另外,CY7C68013内部集成的USB2.0的SIF能完成大部分USB2.0协议的处理工作,从而减少了用户对繁杂的USB协议的处理。

2 硬件设计及原理

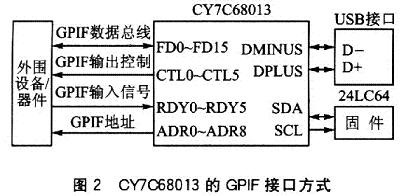

在GPIF接口方式设计中,GPIF作为CY7C68013的端点FIFO的内部控制器,在这种方式下,CPU不会干涉数据的传输。CY7C68013的GPIF接口方式如图2所示。

CY7C68013专门为GPIF提供了接口信号(包括16位数据线、输出控制信号CTL、输入控制信号RDY以及地址线ADR),这些信号负责完成USB接口芯片与外围设备或器件(如FPGA、DSP等)的数据读/写控制和传输。以下为GPIF方式下的主要端口功能。

- FDO~FDl5(输入/输出):USB主机通过CY7C68013与外部设备进行数据传输的数据线,可以用8位或16位数据线。

- CTLO~CTL5(输出):CY7C68013对外部设备进行控制的信号线。

- RDY0~RDY5(输入):CY7C68013对外部设备的状态进行检测的信号线。

- SDA(双向)、SCL(输出):E2PROM的数据及时钟信号线。

- ADR0~ADR8(输出);GPIF为外部设备提供的地址线。

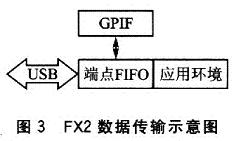

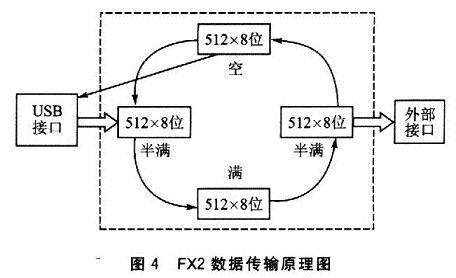

在本设计中,除了重点利用通用可编程接口来实现无缝、高速的传输数据外,还采用了EZ-USBFX2提供的一种独特架构,即“量子FIFO(Quantum FIFO)”处理架构。它能较好地解决带宽问题,图3为其数据传输示意图。当USB执行OUT时,EP2端点被设置为512字节四重FIFO(在USB端和外部接口端,都不知道有四重FIFO),图4为其数据传输原理图。在USB端看来,只要有1个FIFO为“半满”,那么就可以继续发送数据。

当前操作的FIFO写“满”时,FX2自动将其转换到外部接口端,排除等候读取;并将USB接口队列中下一个为“空”的FIFO转移到USB接口上,供其继续写数据。同时,在外部接口端看来,只要有1个FIFO为“半满”,就可以继续读取数据。当前操作的FIFO读“空”时,FX2自动将其转换到USB接口端,排除等候写入;并将外部接口队列中下一个为“满”的FIFO转移到外部接口上,供其继续读取数据。

3 软件设计及实现

本设计的软件设计包括:固件程序、驱动程序和应用程序设计。其中,固件程序是整个程序设计的核心,它在设备CPU中运行。GPIF就是在固件中实现的,因此,只有在该程序运行时,外设才能称之为具有给定功能的外部设备。

3.1 固件设计

在GPIF高速数据传输中,GPIF波形的描述符决定了整个数据传输过程的时序。GPIF波形描述符通常用Cypress公司的GPIF工具(GPIFTOOL)进行配置。它是一个可运行于Windows平台的应用程序,与FX2的开发包一起发布的。在GPIF方式下,所有的读/写及控制逻辑通过CY7C68013的GPIF以软件编程的方式实现,且控制逻辑的变换方便灵活(只需要改变接口的一个配置寄存器的值)。

FX2由4个GPIF波形描述符控制各个状态,它们分别是GPIF Waveform 0(FIFORd)、GPIF Waveform1(FIFOWr)、GPIF Waveform 2(SnglRd)和GPIF Wave-form 3(SnglWr)。这些波形描述符可以动态地配置给任何一个端点FIFO。FX2的固件程序可以把这些描述符配置给4个FIFO中的任意一个;配置后,GPIF将依据波形描述符产生相应的控制逻辑和握手信号给外界接口,以满足向FIFO读/写数据的需要。每个波形描述符包含了7个有效状态(S0~S6)和1个空闲状态。在每个有效状态对应的时间段里,经过预先设置,GPIF可以完成以下几项工作:驱动(使高或低)或浮接CTL输出,采样或驱动FIFO的数据总线,增加GPIF地址总线的值和指向当前FIFO指针的值,以及启动GPIFWF(GPIF波形)中断。除此之外,在每个状态下,GPIF还可以对几个信号(如RDY输入端、FIFO状态标志位、内部RDY标志位和传输计数终止标志位)中的任意两个进行采样,把其中两个信号相“与”、相“或”或者相“异或”,并根据结果跳转到其他任意一个状态或延迟1~256个时钟周期,当然也可以根据输入端的信号进行跳转或延迟。

评论