一旦系统上电, 数字电位器 新颖地被用做逻辑门功能。

本设计方案描述一个典型的使用PAL(可编程逻辑阵列)、GAL(门逻辑阵列)或CPLD(复杂的可编程逻辑设备)实现相对简单的 非易失性 门功能。为控制 逻辑信号 来阻塞或传输逻辑信号,通常使用逻辑门,如与门。使用门的第二个输入来决定门是阻塞还是传输应用信号。因为逻辑门实现直接布尔操作,它们的操作是没有存储器配合的可组合逻辑。

然而,系统启动后,如果设计经常阻塞或传输信号的门,在非易失性存储器的某些形式下,必须存储“传输/阻塞”

的逻辑状态。两个基本方法用于存储这种逻辑状态。第一个使用微处理器结合非易失性存储器,例如EEPROM。如果系统可以等到微处理器从存储器读出逻辑状态,并应用到硬件管脚,如典型的GPIO口,这种方法是适用的。然而,一些系统需要在上电时就传输/阻塞信号。对那些系统,存储器的读延时是不可接受的。

第二种方法用于没有微处理器或启动时微处理器不能等到存储器读出的系统,在启动时存储逻辑状态的设备可用。为了这个目的,采用PAL、GAL和CPLD设备结合可编程非易失性存储器实现控制功能。然而,这些设备提供更多存储器控制和不需要门的特殊系统。它们的封装也相当大到足以容纳许多逻辑I/O引脚。

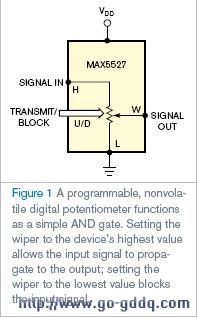

如果不需要非易失性门,考虑使用器件共用在模拟和混合信号系统中:数字电位器(图1)。将电阻线的L端接地,信号由H端接入回路。然后,输出触点短接到地阻塞或连接到输入信号传输。

单板或系统测试期间,通过串行接口为数字电位器编程。一些数字电位器的通讯接口适于这个目的。当选择非易失性数字电位器时,应考虑以下标准:

数字电位器典型有32或更多抽头;至少需要两个。一个数字电位器触点有与内部开关相结合的电阻,应该尽可能小来避免干扰开关信号。典型触点电阻为100Ω到1kΩ。对Maxim的MAX5527而言,触点电阻为90Ω。

因为数字电位器触点电阻随供电电源增长而减少,应该选择高供电电压。

为减小信号源负载和不限制电位器信号带宽,应选择高端局间电阻设备;在许多应用中,100 kΩ是可以接受的。

如果必须用易失性存储器给门状态编程,选择非易失性数字电位器。一些数字电位器是OTP(一次性编程);这个特征允许保存触点设置。当不希望控制功能改变时,使用OTP特征是适当的。状态需被存储的门的数量决定所需的电位器数量。可用作每个封装一到六个或更多阵列。

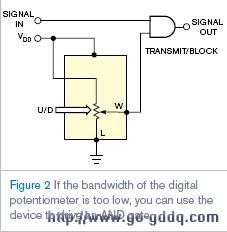

数字电位器的带宽决定信号通过电位器传输的最大数据率。如果这些应用逻辑信号的开关率对使用的电位器过高,可以使用带数字电位器控制传输/阻塞输入的传统高速逻辑门(图2)。

评论